Този

раздел е нов.

Създаден е

през 2022 година.

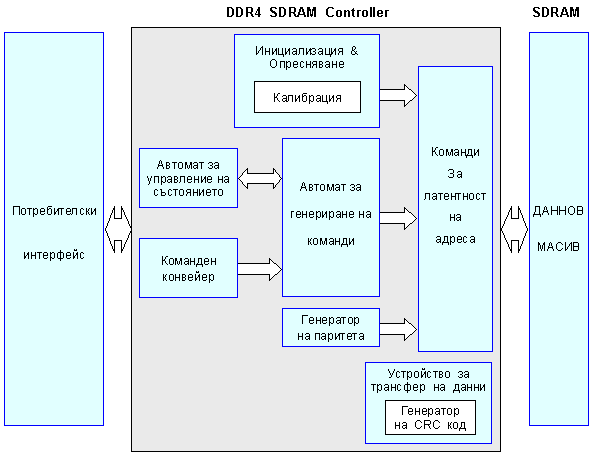

4.2.2.1. Контролер

на

съвременни

динамични

памети

DDR4 SDRAM е съкращение за синхронна динамична памет с произволен достъп, изпълнена по технологията Xn-Prefetch, която осветлихме подробно в раздел 4.2.2 и неговото Продължение. Тази памет е предназначена най-вече за компютърни, сървърни, биомедицински и вградени приложения. Нарастващото търсене на по-бързи операционни системи, както и приложения с голям размер създадоха необходимостта от използване на памет с голям капацитет. Поради използването на памет с голям капацитет, консумацията на енергия също се увеличава значително, което е един от основните проблеми на пазара на памет. DDR4, както и следващите поколения памети на тази технология, не само увеличи обема си, но и намали консумацията на енергия.

Основните

характеристики

в DDR4 се отнасят

до:

·

Захранващо

напрежение ;

·

По-висока

скорост на

данни ;

·

По-висока

плътност ;

·

Повече

банки ;

·

По-бърз

достъп до

пакети ;

·

По-висока

надеждност

на системата

в сравнение с

DDR3.

В DDR4 SDRAM са въведени нови функции като: CRC, C/A паритет, инверсия на шината на данни (DBI), латентност на командния адрес (CAL), адресируемост на DRAM, CAL (закъснение на командния адрес), MPR (многофункционални регистри), режим на предавка, FGREF (опресняване на фина грануларност) и опресняване с контролирана температура. Сред тях CRC, C/A паритет, инверсия на шината на данни (DBI) са предназначени за решаване на проблема с надеждността на данните.

В следващата таблица са представени за сравнение някои параметри на DDR4 с DDR3.

|

Параметри |

DDR3 |

DDR4 |

Предимства

|

|

Захранване |

1,5 [v] |

1,2 [v] |

Снижена

ел. мощност |

|

Кратност

на

трансфера (Prefetch) |

8n |

8n |

DDR4 има 8 кратен

паралелен

трансфер

както и

паралелна

банкова

структура |

|

Плътност

(Densities) |

512 [Mib] –

8 [Gib] |

2 [Gib] – 16 [Gib] |

По-добро

разрешение

за

подсистеми

с голям капацитет |

|

Скорост

на данните [MT/s] |

800, 1066, 1333, 1600, 1866, 2133 |

1600, 1866, 2133, 2400, 2667, 3200 |

Миграция

към

по-висока

честотна

лента на данни |

|

Брой на

вътрешните

банки |

8 |

16 |

Повече

банки |

|

Брой на

групите от

банки |

0 |

4 |

По-бърз

пакетен

достъп |

DDR4

контролерът

се използва

като мост при

взаимодействие

на паметта с

процесорната

подсистема.

Той

управлява

двупосочния

поток от

данни на

паметта.

Основната

функция на

контролера е

четене и

запис на

данни. Той

също така помага

на DRAM да запази

данните като

периодично я

опреснява,

изпълнява

изпреварващо

зареждане и

т.н.

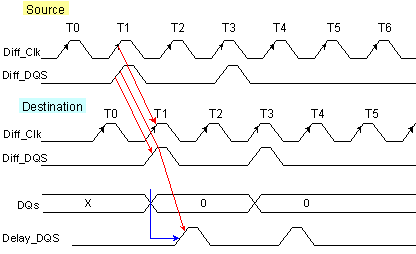

Прехвърлянето

на данни се

синхронизира

с двупосочен

парафазен

строб за данни

DQS, и not(DQS (Data Queue Strobe) (разгледайте

фигура 4.2.2.17

и

поясняващия

ѝ текстове).

Управлението

на DDR

паметта

издава строб

на данни (DQS) за

операция за

четене, а

устройство,

подаващо

данни, издава

строб DQS за

операция

запис.

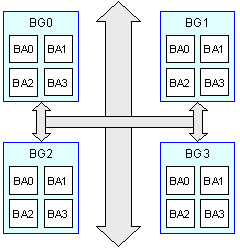

Функционално описание и структура на DDR4

DDR4 има 8 кратен

трансфер с

предварително

извличане (8n Preface) и 4

паралелни

банки за

по-висока

скорост на трансфер

на данни.

Вътрешното

конфигуриране

е в 4 банкови

групи с по 4

банки във

всяка банкова

група (вижте фигура 4.2.2.40).

Банката е

независим

масив от памет.

Адресът на

реда и

адресът на

колоната се

използват за

намиране на

искания

адрес в банката.

Страницата

има уникален

адрес, който

се състои от

номер на

банкова

група, номер

на банка и

адрес на ред.

Размерът на

страницата е

общ брой

колони в един

ред. Структурата

на

архитектура

способства

за подобряване

на скоростта

за трансфер

на данни, без

увеличаване

на дължината

на пакета е

пояснена със

следната

рисунка:

Фиг. 4.2.2.1.1. Организация

на RAM

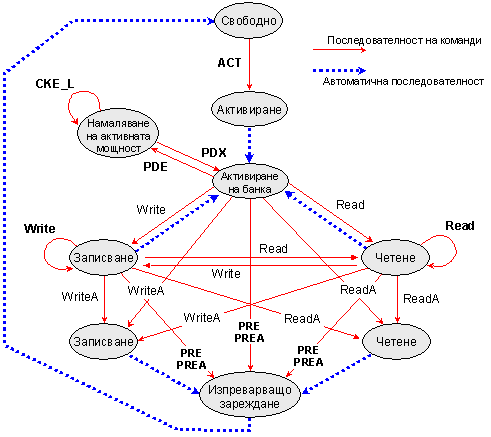

Следващата

фигура

представя

графа на

преходите и

състоянията

на динамичната

памет.

Показани са и

командите за

преход между

състоянията

при

управление

на паметта.

Фиг. 4.2.2.1.2. Граф

на

състоянията

на DDR4

А. Автомата за управление на състоянието на групата

Както

се вижда, в

контролера

съществува

автомат за

управление

на банките.

Той следи текущото

състояние на

всяка банка

памет в данновия

масив на DRAM.

Това

осигурява

по-голяма

гъвкавост за

извършване

на паралелна

обработка на

командите за

четене и

запис.

Автоматът е

паралелно

свързан с

всички банки,

както е

показано на

следващата

фигура.

Фиг. 4.2.2.1.3. Обща

структура на

контролера

на DDR4

Има

4 автомата за

състоянието

на банкови групи

и всяка

банкова

група

съдържа 4

автомата за

състоянието

на всяка

банка, така

че общо 16-те

банки могат

да се

управляват

едновременно.

Всеки

автомат за

състояние

съдържа

специфичен

брояч на

времето, като

tCCD, tRRD, tFAW и т.н.

Състоянието

може да бъде:

·

Банката

е активна ;

·

Банката

е достъпна за

четене ;

·

Банката

е достъпна за

запис ;

·

Предварителна

промяна и

адрес на ред.

Това

гарантира:

·

Времето

за

превключване

на шината за

четене-запис

и за

запис-четене

;

·

Активиране

на

предварителното

зареждане ;

·

Активиране

на

латентността

между различните

банки и

банкови

групи.

Когато

се изпрати

команда към DDR4

броячите на

ограничението

на времето,

съответстващи

на тази

команда,

започват да

отброяват и актуализират

състоянието.

Например, ако

банка “x” в DDR4 е в

състояние на

неактивност

и се издава

команда за активиране

на DDR4,

времевите

ограничения,

свързани с

командата,

са:

·

tRRD

(закъснение

на командата

от активна

към активна) ;

·

tRCD

(закъснение

от активно за

четене/запис

;

·

tRAS

(закъснение

от активно

към

предварително

зареждане) и

т.н.

След издаване на команда за активиране автоматът на състоянието на съответната банка “x” започва да отброява тези времена, т.е. tRRD, tRCD, tRAS и т.н.,.

В

началото

статусът на

банката “x” е:

активност на

банката=0,

готовност за

четене=0,

готовност за

записване=0,

готовност за

предварителна

промяна=0.

След като

времето tRCD

започне да се

отброява, състоянието

на банката „x“

се

актуализира

така: банката

е активна=1,

банката е

готова за четене=1,

банката е

готова за

записване=1,

банката е

готова за

изпреварващ

обмен=0.

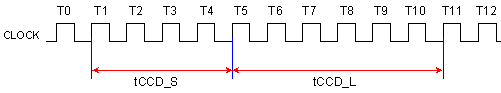

DDR4 въвежда нови спецификации за четене-четене или забавяне на запис-запис, които се наричат tCCD_S и tCCD_L, както и време за четене или запис до банки от различни банкови групи и същите банкови групи съответно.

Фиг. 4.2.2.1.4. Вариации

на tCCD

Пълната

честотна

лента на DDR4 не

може да се използва,

докато не се

използва

преплитащ достъп

до банкова

група. За

да постигне

по-добра

производителност,

контролерът

може да

изпълнява

операциите

за

преплитане

на банки,

като

наблюдава статуса

на ранга.

Б. CMD конвейер (команден конвейер)

Съвременните системи в голяма степен споделят общата RAM памет (като няколко процесора, GPU, GPIO споделят DRAM). Така контролерът нарежда на опашка множество команди от различни периферни устройства, използвайки команден конвейер. Командният конвейер се използва за оптимално оползотворяване на честотната лента. Командният конвейер се използва от блока за генериране на команди за предварителна обработка на целевата банка за операция за четене или запис, като например извършва активно и предварително зареждане.

В. Закъснение на адреса на командата

Функцията

CAL (Command-to-Address Latency) се

предлага за DDR4

памет, в

която е

възможно пестене

на енергия.

По принцип CAL е

закъснението

между

активиране

на избрания

чип и появата

на

команда/адрес

в брой тактови

цикли, което

се дефинира

от регистъра

на режима.

Преди да

издаде

команда, контролерът

предоставя

това време на

DRAM за активиране

на CMD/ADDR

приемниците.

Приемниците

могат да

бъдат

заключени,

когато командата

и адресът са

заключени. В

случай на подаване

на

последователни

команди,

приемникът

ще бъде

активиран от

DRAM за периода

на командната

последователност.

Г. Калибрираща единица

Устройството

за

калибриране

извършва изравняване

на запис,

изравняване

на четене и

калибриране

на ZQ. DDR4 паметта

използва

специална

топология (fly-by), целяща

по-добър

интегритет

на сигнала.

За да реши

проблема с

изкривяването,

контролерът

на паметта

използва

функцията за

"изравняване

за запис“ (write leveling) и

обратна връзка

от DDR4, за да

настрои

данновия

строб към тактовия

сигнал. Тази

функция може

да компенсира

небалансираното

натоварване

на платката

за операции

запис и

четене.

Устройството

за

калибриране

поставя DDR4 в

състояние на

изравняване

при запис

чрез заявен

режим на

запис в

регистър MR1 на

DDR4.

Стробът

на запис DQS

многократно

се забавя на

малки стъпки

от Delay Locked Loop (DLL). DDR4

синхронизира

предния

фронт на

сигнала DQS по

предния

фронт на CLK и

предоставя

обратна връзка

за DQ. По време

на този

протокол всеки

набор от DQ се

извежда с “0“,

докато

нарастващият

фронт не бъде

открит от DQS, в

който момент

DQ ще бъде

изведен с “1“.

Устройството

за калибриране

ще открие

тези “1“ на DQ

шината и след

това ще знае

правилната DQS

компенсация,

за да подравни

DQS и CLK по пътя за

запис. След

като всички DQS

са коригирани,

тези

компенсационни

стойности на

DLL се

съхраняват

за всеки DQS за

бъдеща

употреба.

След това

контролерът

на паметта

изпраща

друга MRS

команда за

излизане от

режима на ниво

на запис.

Фиг. 4.2.2.1.5. Изравняване

при запис (write leveling)

В

DDR4

изравняването

при запис и

при четене се

управлява

чрез

сигналите DQS/DQ.

Изравняването

при четене

компенсира

небалансираното

натоварване

на пътя за

четене.

Първо, контролерът

на паметта

поставя

устройствата

с памет в DDR4 в режим

MPR, като

записва в

регистъра MR3.

Така поставя

устройствата

с памет в DDR4 в

режим на изравняване

при четене,

който

извежда

тренировъчен

модел от

последователни

“01“ при всяка команда

за четене.

Тъй като

контролерът

на паметта

знае този

поток от данни,

той ще

коригира

вътрешното

забавяне на DQS,

за да улови DQ с

помощта на DQS.

Контролерът на

паметта

повтаря тези

показания за

калибриране,

докато

улавлението

на прочетени данни

в контролера

на паметта не

бъде

оптимизирано.

Командата ZQ Calibration се използва за калибриране на стойностите на DRAM Ron & ODT. ZQ калибрирането отчита вариацията на напрежението и температурата на изходния драйвер на DRAM.

Е. Блок за генериране на команди

Генераторът на команди приема потребителски команди от конвейерния блок. Когато модулът получи единична заявка от конвейера, тя се обработва незабавно. При заявка за четене или за запис, устройството за генериране на команди търси калибрираща единица, за да се гарантира, че ограниченията във времето за всяка предишна транзакция с памет са изпълнени преди стартиране на новата транзакция. CMD генераторът също така проверява за наличност на целева банка за операция четене или запис от статуса на ранг. Наличност на банка означава, че исканият ред в съответната банка, е активен. Ако исканата банка не е активна, тогава тя генерира необходимата команда за предварително зареждане както и активна команда за активиране на банката в DDR4. Генерирането на команди се спира от изхвърлянето на следващата команда, докато не бъдат изпълнени изискванията за време на SRAM. При наличност на банката, заявената команда за четене или запис се изпраща до SRAM и до вътрешния автомат за статус на ранг, така че рангът да може да се актуализира всеки път, когато се изпраща нова команда. Докато обработва активната заявка от конвейера, ако има някакви неудовлетворени времеви ограничения, то те карат контролера да блокира транзакцията. След това контролерът проверява следващата предстояща заявка в опашката. CMD генераторът проверява адреса на следващата банка за заявки, за да разбере дали следващата заявена банка е активна и дали активираният ред съвпада с адреса на искания ред. Ако условието не е изпълнено, тогава генераторът на команди изпълнява необходимата последователност за активиране на предварително зареждане, за да активира тази банка, така че когато заявката е активна, да има минимално време за спиране. Такива умишлено активни банки за бъдещи заявки използват времето за задържане на активните заявки. Това опортюнистично гледане напред подобрява общата пропускателна способност.

Ж. Блок за трансфер на данни

Устройството

за трансфер

на данни се

състои от

FIFO-опашка за

четене и

FIFO-опашка за

запис. Прочетените

от FIFO данни се

предават на

потребителя.

FIFO за запис

получава

данни за

запис от

потребителския

интерфейс.

Прочетените

от паметта

данни

пристигат в

контролера

както на положителния,

така и на

отрицателния

фронт на

тактовата

последователност.

Дължината на

пакета на е 8. Read FIFO

улавя тези

данни в 4

тактови

цикъла и

предоставя

на потребителя

прочетени

данни в един

тактов цикъл

по следващия

положителен

фронт на

тактовия сигнал.

По подобен

начин Write

FIFO зарежда

данните за

запис от

потребителя в

един такт и

изпраща към

паметта в

следващите 4

такта както

на

положителен,

така и на

отрицателен

фронт. По

време на

прехвърлянето

на данни за

запис към DDR4

контролерът

също добавя CRC

код като

следа от

всеки пакет.

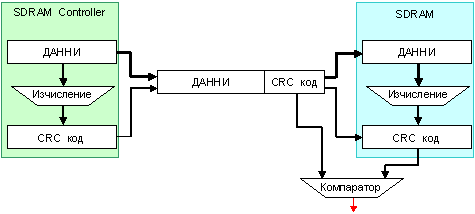

З. CRC генератор (CRC – Cyclic Redundancy Check)

С

увеличаване

на скоростта

данните са

склонни към

грешки. За да

разреши

проблема с надеждността

на данните по

време на

операции WRITE, DDR4

включва

циклична

проверка на

излишък (CRC). DDR4

използва

8-битов

контрол за

грешки в

заглавката

на CRC. CRC

полиномът,

използван от

DDR4, е ATM-8 HEC, т.е.

![]()

Фиг.

4.2.2.1.6. CRC генератор

и контрол

Фигурата

по-горе

показва

схемата за

проверка на

вътрешния

трансфер. DRAM

генерира

контролна

сума за всеки

пакет за

запис. CRC

генераторът

използва 72

бита данни (64+8=72). DRAM

сравнява

контролната

сума. Ако две

контролни

суми не

съвпадат,

тогава DRAM

сигнализира

за грешка.

И. Инициализация и опресняване

Устройството

за

инициализация

и опресняване

извършва

инициализация

на захранването

и периодично

опресняване.

След

включване

или нулиране,

DDR4 трябва да бъде

инициализиран,

преди да

започне

транзакция

за четене или

запис. Пинът

(изводът) за нулиране

(reset) на DDR4

следва да се

задържи в

ниско ниво в

продължение

на 100 [ns], за да

започне

процеса на

инициализация.

За

активирате

тактовия

генератор в DDR4,

на извода reset подайте

високо ниво,

а на извод CKE

подайте ниско

ниво в

продължение

на 5100 [ns]. След това

на извод CKE

подайте

високо ниво.

След

интервал tXPR,

когато DRAM се

инициализира,

се издават

команди Mode Register Set

за

установяване

на

подходящия режим

на работа,

дължина на

пакета,

адитивна латентност,

касационна

латентност и

т.н. След като

зададете

режима,

регистрирайте

превключвателя

на модула за

инициализация

и опресняване

на модула за

калибриране,

за да

извършите

изравняване

на четене и запис.

След

завършване DDR4

е готова за

нормална

работа.

Съществува

брояч tREFI, който

отчита интервала

за

опресняване

на DDR4. При всяко

отброяване

на tREFI,

контролерът

издава

команда за

опресняване

на DDR4.

Следващият

раздел е:

4.2.3.

Полупроводникови

флаш памети