Последната

актуализация

на този

раздел е от 2019

година.

4.2.3.

Полупроводникови

флаш памети –

Flash-Memory.

Архитектура NOR.

Архитектура NAND.

Архитектура 3D-NAND

Флаш (Flash)

паметите са

отделен вид

EEPROM-памети

(електрически

изтриващи се

енергонезависими

памети). В

началния

пункт на тази

глава този

вид памет

беше

съответно

класифициран

и нейните

основни

особености

бяха

разяснени.

Първите флаш

памети са

изобретени

през 1984 година

от

сътрудници

на фирмата Toshiba.

Изобретателите

на този тип

памет са били

впечатлени

от скоростта,

с която се

изтривало

съдържанието

й, откъдето

произлиза и

наименованието

й (in a flash – в един

миг, т.е.

светкавично).

Много от

големите

производители

са се

опитвали да

наложат свои

имена, но все

пак тази дума

доминира в

съвременните

наименования.

Първите

масово

произвеждани

интегрални схеми

флаш памет от

тип NOR

предлага

през 1988 година

фирмата Intel.

Флаш памет с

архитектура NAND

е предложена

за първи път

от Toshiba през 1989

година Тя се

е

конкурирала

с по-висока

скорост на

запис и по-малка

площ на чипа.

Особеното

във флаш

паметта е

технологията

за

построяване

на нейните

запомнящи

елементи,

наречени Stacked Gate Cell,

които

представляват

полеви

транзистори с

многослоен

гейт.

Запомнящите

клетки се изграждат

основно като

два типа

схеми:

·

Структура

SLC (Single-level Cell).

Запомнящата

клетка има

едно ниво на

наситеност,

т.е.

съхранява

кода на един

бит (0 или1).

·

Структура

MLC (Multi-level Cell).

Запомняща

клетка с

няколко нива

на наситеност,

позволяващи

кодирано

съхранение

на повече от

един бит

(обикновено 2,

т.е. 00, 01, 10, 11).

Основните

характеристики

на този тип

памет е

по-голям обем

при същата

площ върху

кристала, но

за сметка на

по-бавен

достъп и

по-малко

полезни

работни цикли

на запис

(изтриване) –

примерно

около10000;

И в

двата типа

запомнящи

елементи

единицата (1)

се кодира с

отсъствие на

електрически

заряд.

Структурата

MLC има своето

развитие и

вече са

известни и се

прилагат

следните

структури:

·

Структура

TLC (Triple-level Cell).

Запомнящата

клетка

съхранява

три бита (осем

нива на

наситеност).

Тази

структура е

предложена през

2009 г. от Toshiba. През 2010

г. Samsung започва

масово

производство

на тази структура,

като го

внедрява в

своите SSD

устройства.

·

Структура

QLC (Quadruple-level Cell).

Запомнящата

клетка

съхранява

четири бита (16

нива на

наситеност).

През 2009 г. Toshiba и SanDisk

представиха

чип NAND флаш

памет от този

тип, с капацитет

от 64[Gib]. През 2018 г. Toshiba

представи

чипове от този

тип клетки, с

обем над 700[Gib].

В

основата на

този тип

памети стои

активният

електронен

елемент,

определен

като полеви

транзистор,

по тази

причина

нашето

изложение не може

да не се спре

на неговата

конструкция и

на неговото

приложение.

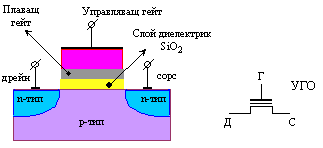

Структура на MOS-транзистор

За да се разбира и използва този тип памет, трябва добре да се познава природата на нейното свойство паметливост, така че тук ще се постараем да я поясним. Между флаш паметта и динамичната памет, а така също и ROM-паметта, има нещо много общо. Принципната разлика обаче се състои най-вече в строежа на запомнящия елемент. Ако в динамичната памет това е кондензаторът, то във флаш паметта това е споменатият вече MOS-транзистор със специална структура, която ще представим.

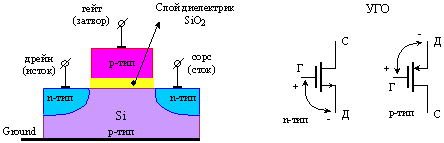

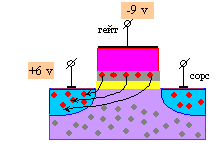

Обикновеният

MOS-транзистор,

за който вече

писахме в

раздел 4.2.1, има 3

извода

(електрода) – сток,

исток и затвор

(или още сорс

- source, дрейн - drain

и гейт - gate).

Тук ние ще си

позволим да

употребяваме

и двата вида

наименования.

Фиг. 4.2.3.1. Структура

на n-p-n MOS

транзистор

MOS-транзисторът

може да се

намира в две

състояния –

отворено и

затворено.

Става дума за

канала между

дрейна и

сорса, по

който

протича (или не

протича) ток.

Наименованията

на тези два извода

напомнят

откъде

излизат и

накъде отиват

носителите

на

електричество

Както се

вижда от

рисунката,

тези два

извода са раздалечени

един от друг,

а върху

ивицата между

тях е

позициониран

управляващият

извод (гейт,

затвор). В

този смисъл

конструкцията

наподобява

кондензатор.

Съществуват два

вида

MOS-транзистори:

с n-канал

и с р-канал

(според

основните

носители на

електричество).

Условните

графични

означения на

тези електронни

елементи са

показани в

дясната част

на рисунката.

В

MOS-транзистора

с n-канал, n-проводимите

области на

сорса и на

дрейна имат

електронна

проводимост,

а р-областта

на гейта –

дупчеста

проводимост

(и обратно).

Самият

транзистор е

технологично

изграден

върху

полупроводникова

подложка с р-проводимост.

Гейтът

геометрически

се намира

между сорса и

дрейна и е

отделен от

тях с много

тънък слой

изолатор

(диелектрик SiO2).

Дебелината

на този

изолиращ

слой е не повече

от 90[nm]. По тази

причина

гайтът

(затворът) се

нарича изолиран.

Електрическото

поле обаче,

което се

образува

между гейта и

подложката е

в състояние да

създава и да

управлява

проводимия

канал, който

се образува

между дрейна

(истока) и сорса

(стока).

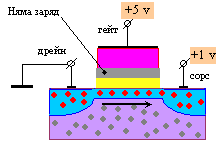

Ще

разгледаме

принципът на

действие на

този

транзистор

върху

неговия n-p-n

вариант. При

електрическо

свързване на

транзистора,

подложката,

върху която е

реализиран, е

подключена

към общата

маса. Ако на

сорса се

приложи

положителен

потенциал и

общата маса

върху дрейна,

то в резултат

на това, за

сметка на

дифузията на

дупки от

р-областта в

n-областта и

на обратната

дифузия на

електрони от

n-областта в

р-областта,

на границата

между тези

области се

образуват

тънки

обеднени на

основни

носители

слоеве, които

възпрепятстват

протичането

на ток между

дрейна и

сорса, т.е.

транзисторът

се намира в

запушено

състояние.

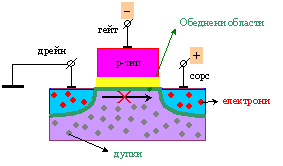

Фиг. 4.2.3.2. Запушен

транзистор

Така в обикновено състояние, когато към гейта не е подадено напрежение или е подаден отрицателен потенциал спрямо масата, транзисторът, както вече споменахме, се намира в запушено състояние. В това състояние той не способен да провежда ток от дрейна към сорса. Състоянието не се променя даже когато между тези два електрода се приложи напрежение (при това нямаме предвид обратните токове, които възникват от движението на неосновните носители на заряд под въздействието на електрическите полета, т.е. на дупки в областите с n-проводимост и електрони в областта с р-проводимост).

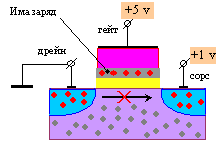

Ако

обаче към

гейта се

приложи

положителен

потенциал

ситуацията

коренно се

променя. Под

въздействието

на това

допълнително

поле (гейт /

подложка). Приложено

в областта на

затвора

дупките, които

се намират в

неговата

област се

отблъскват в

дълбочина на

подложката, а

електроните

се засмукват

в тази

област,

образувайки

при това

силно

обогатен на

отрицателни

носители

(заряд) канал

между дрейна

и сорса.

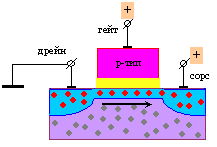

Фиг. 4.2.3.3. Отпушен

транзистор

В това

състояние

през

транзистора

протича ток,

т.е. той е в

отпушено

състояние.

Ако

напрежението

на гейта падне

транзисторът

се запушва

отново, тъй

като

проводящият

канал се

разрушава.

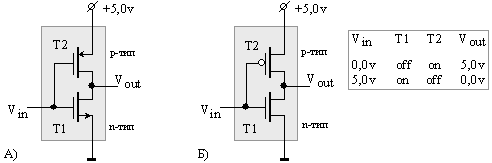

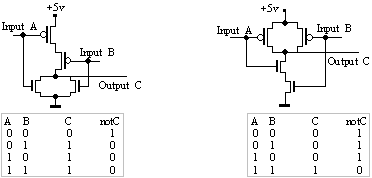

Съвместното

свързване и

използване

на два

транзистора

с различна

проводимост

е известно

под

наименованието

комплементарно.

Такава

транзисторна

двойка

(фигура 4.2.3.4) се

нарича CMOS и

имитира

логическата

функция

отрицание

(инвертиране)

на входния

сигнал. В

таблицата се

вижда при

какво входно

напрежение

кой от транзисторите

е включен и

кой изключен

и какво е изходното

напрежение.

Когато транзисторът

се намира в

отпушено

състояние между

сорса и

дрейна е

близко до

нулата, а когато

транзисторът

се намира в

запушено състояние

то е почти

равно на

приложеното

към сорса.

Тази

ситуация

може да се

оприличи на

ключ, който

се включва и

изключва.

Фиг. 4.2.3.4. CMOS-инвертор

На пръв поглед работата на транзистора може да се приеме като работа на запомнящ елемент, но тук има един проблем. Той се състои в това, че за да се управлява състоянието на транзистора на гейта трябва да се подава напрежение, т.е. тази структура позволява да се изпълнява запис на информация (да се задава значение “0” или “1”), но не позволява съхраняването на информацията при отключване на захранването, тъй като без захранване (без положителен потенциал на гейта) състоянието на транзистора е винаги запушено.

Възможни са още следните електронни схеми на логически елементи:

Фиг. 4.2.3.5. Логически

елементи OR (NOR) и AND

(NAND)

Така се появява задачата за създаване на такава структура, щото състоянието (информацията) на транзистора да се съхранява във всички случаи неограничено дълго време. Решението на задачата е постигнато чрез изграждане в структурата на транзистора на допълнителен гейт, служещ за съхранение на електрически заряд (от електрони), във времето.

Структура на MOS-транзистор с плаващ гейт

Както

се вижда от

рисунката на

фигура 4.2.3.6, в р-проводимата

област на

управляващия

(Control) гейт е

изграден

плаващият (Floating)

гейт, който

представлява

n-проводим

слой, нанесен

върху много

тънък слой

диелектрик

(изолатор) SiО2

. Дебелината

на

изолиращия

слой е от

порядъка на 10[nm].

Фиг. 4.2.3.6. Структура

на

транзистор с

плаващ гейт и

условно

графично

означение

Ако

върху

плаващият

гейт няма

отложени

електрони, то

транзисторът

се държи като

вече

описания

обикновен MOS

транзистор.

При

инициализация

на паметта,

т.е. при

подаване на

положително

напрежение на

управляващия

гейт на всеки

транзистор, същият

ще се отвори

и ще остане в

това състояние,

а то

съответства

на логическа

нула – “0”. Положителното

напрежение

на гейта

отблъсква

дупчестите

носители на

електричество

в областта

под него и

способства

за протичане

на ток между

истока и

стока -

положение, което

се нарича

отворено.

Ако в

плаващият

гейт има

отложени

(натрупани)

електрони, които

създават

отрицателен

полюс, тогава

транзисторът

е запушен,

тъй като в

зоната под него

се привличат

положителните

носители на

ток, с което

се

възпрепятстват

свободните

електрони.

Това

състояние се

интерпретира

като

логическа

единица – “1”.

Описаните

две състояния

на

транзистора

са

илюстрирани

на фигура 4.2.3.7.

Тук

отново

следва да

обърнем

внимание на читателя,

че

показаните в

рисунките

захранващи

напрежения,

материали и

самата структура

на

транзистора,

следва да се

възприемат

само като

примерни.

Това е така,

защото

производствените

технологии

са в

непрекъснато

развитие и

всички технически

параметри на

интегралните

електронни

елементи са в

непрекъснато

изменение,

което се

отнася и до

вижданията и

на отделните

производители.

Фиг. 4.2.3.7. Отпушен

(“0”) и запушен (“1”)

транзистор

(четене

на

съдържанието

от

запомнящия

елемент)

Ако обаче в плаващият гейт са натрупани излишно количество носители (електрони), то зарядът му е силно отрицателен и при подаване на положително напрежение на управляващия гейт (при инициализация) транзисторът ще продължава да бъде запушен. С други думи, ако инициализиращото напрежение не компенсира полето от плаващия гейт върху тънкия изолационен слой на прехода между дрейна и сорса, то транзисторът ще запазва състоянието си. По този начин установяваме, че отсъствието или наличието на заряд върху плаващия гейт еднозначно определя състоянието на транзистора (отпушен или запушен) при подаване на едно и също положително напрежение върху управляващия гейт. Ако подаването на положително напрежение към управляващия гейт интерпретираме като инициализация на клетка от паметта, то по възникналото между дрейна и сорса напрежение може да съдим за наличието или за отсъствието на заряд върху плаващия гейт, с други думи да бъде прочетено неговото състояние. Така транзисторът с плаващ гейт може да играе ролята на запомнящ елемент (един бит). Важното в случая е това, че електрическият заряд върху плаващия гейт (ако той там въобще съществува) може да се съхранява неограничено дълго време както при наличие така и при отсъствие на инициализиращото напрежение върху управляващия гейт. Такава клетка от паметта е вече енергонезависима. В този план на разсъждения остава да обясним как се извършва запис в запомнящия елемент, т.е. как се натрупва и съответно разсейва зарядът върху плаващия гейт на транзистора.

Натрупването

на заряд

върху

плаващия гейт

(процес на

запис) се

реализира

или чрез

метода на

инжекция на

горещи електрони

(CHE - channel hot electrons) или

чрез метода

на

квантово-механическия

тунелен

ефект на

Фаулер-Нордхайм

(Fowler-Nordheim), който се

нарича още

процес на

пробив, или FN-метод.

При

метода на

инжекция на

горещи

електрони

(CHE-метод), на

сорса и на

управляващия

гейт се

подава

високо

напрежение,

което е

необходимо

за

ускоряване

на електроните

до степен,

при която те

вече могат да

преодолеят

потенциалната

бариера на

тънкия

изолационен

слой (да го

тунелират

или “пробият”)

и да

достигнат

областта на

плаващия

гейт.

Ефективността

на този

процес обаче не

е голяма и за

постигане на

желания

ефект се

налага да се

приложи

значително

по-високо

напрежение

(двойно

по-високо),

така че между

дрейна и

сорса да

протече ток

от порядъка

на 1[mA].

Тунелният

ефект се

дължи на

вълновите

свойства на

електрона.

Електронът

няма енергията,

с която да

преодолее

изолационния

слой, но

подпомогнат

от

съответното

напрежение,

той може да

прескочи

диелектрика

и да попадне

в плаващия

гейт. По същество

електронът

преодолява

тънката потенциална

бариера

между

плаващия

гейт и подложката,

създавайки

при това ток

на зареждане.

При FN-метода

не се налага

използването

на високо

напрежение, в

резултат на

което запомнящите

клетки могат

да имат

по-малки размери.

Програмирането

на клетките

при този метод

обаче е

по-бавен

процес.

За да

се премахне

натрупания в

плаващия гейт

заряд на

управляващия

гейт се

подава високо

отрицателно

напрежение, а

на дрейна положително.

С това се

създава

силно обратно

електростатично

поле и

електроните

се изсмукват

(изгонват) от

плаващия

гейт, т.е. те

тунелират

обратно.

Процесът се

нарича

изтриване.

Фиг. 4.2.3.8. Процес

на запис на “1” и

на изтриване

(запис на“0”)

Изложеното

показа как

може да се

управлява

флаш

елемента. За

съжаление

еднотранзисторният

елемент има

редица

недостатъци,

като един от

най-съществените

е лошата мащабируемост.

Проблемът се

изразява в

това, че поради

големите

стойности на

управляващите

напрежения

свързващите

проводници в

интегралната

схема трябва

да се

достатъчно

раздалечени,

което води до

неефективно

усвояване на

площта на кристала,

а от там до

ограничени

обеми на флаш

паметта. Друг

недостатък

на

еднотранзисторният

елемент се

проявява при

записа на

логическа нула.

Тогава върху

плаващия

гейт е

възможно да

се получи

остатъчен

положителен

заряд, което

прави

транзистора

винаги

отпушен.

За

отстраняване

на

недостатъците

се правят

различни

модификации

на флаш

елемента. Така

например

фирмата Silicon Storage Technology

(SST) е

разработила

технология,

при която

гейтовете на

флаш

транзистора

имат

специална форма

и

разположение,

както

показва

следната

фотография:

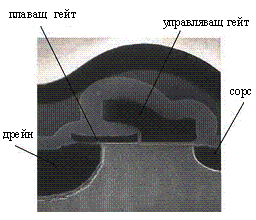

Фиг. 4.2.3.9. Структура

на

полупроводникова

SST-клетка

Извитите

форми на

гейтовете и

припокриването

на плаващия

гейт с

управляващия

е позволило

работните

условия на

процесите в транзистора

да бъдат

значително

облекчени, а

управляващите

напрежения

занижени. Разсейването

на

електроните

от плаващия

гейт става

чрез

подаване на

положително

напрежение

на

управляващия

гейт. Електроните

тунелират не

към дрейна, а

към управляващия

гейт, за

което

спомага и

извитата форма

на двата

гейта. За

натрупване

на заряд

върху

плаващия

гейт към

дрейна и към

управляващия

гейт се

подава

положително

напрежение, а

към сорса –

маса. В

управляващия

гейт се

формира

проводящ

канал, а

напрежението

между дрейна

и сорса

ускорява

електроните

така, че те

преодоляват

потенциалната

бариера и

правят

пробив към

плаващия

гейт. Тази конструкция

и управление

на SST-клетката

водят и до

по-различна

организация

на данновия

масив във

флаш паметта.

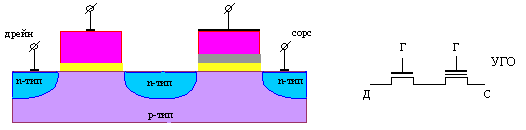

Вторият

вариант,

който ще

разгледаме, е

двутранзисторната

схема –

фигура 4.2.3.10, в

която обикновен

MOS транзистор

се използва

за изолация

на флаш

транзистора

от данновата

линия.

Фиг. 4.2.3.10. Двутранзисторен

флаш елемент

и условно графично

означение

Допълнителният

транзистор

позволява изолация

на флаш

транзистора

от данновата

линия, което

води до

подобряване

на мащабируемостта.

Освен това,

предимство получава

записът въз

основа на

тунелния пробив,

тъй като при

този метод

може да се

работи със

значително

по-ниски

напрежения.

Двутранзисторният

флаш елемент

е в основата

на така

наречената NAND

архитектура.

Третият

вид флаш

елемент,

който ще

споменем, е

известен

като Intel StrataFlash.

Това е флаш

елемент

способен да

натрупва различни

(контролируеми)

количества

заряд върху

плаващия

гейт. Флаш

елементът се

определя

като MCL-клетка (MultiLevel

Cell). Същността

на този вид

елемент се

състои в

това, че чрез

различни

нива на

управляващите

напрежения,

може достатъчно

точно да се

натрупва

върху плаващия

гейт

различни и

ясно

различаващи

се количества

заряд.

Например, за

различаване

върху този

гейт на два

бита

информация

са необходими

4 прагови

нива на

напрежение.

MCL-клетката

на Intel не е

единствената

MCL-клетка.

Фирмата Saifun от

Израел

предлага

NROM-клетката (Nitrid ROM).

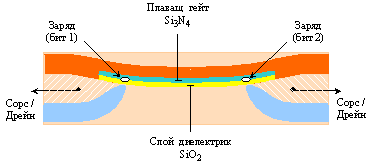

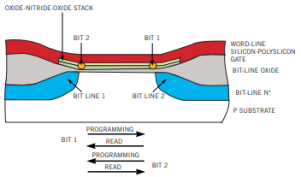

На фигура 4.2.3.9 е

представен

общ вид на

структурата

на този

елемент. Тя,

както се

вижда, е симетрична.

Проводящите

области

(сорс, дрейн)

си разменят

ролите по

време на

управлението.

В матрицата

на

запомнящия

масив на

паметта управляващият

гейт се

свързва

адресната

линия на

реда, а

сорсът и

дрейнът – към

две различни

даннови

линии. В

структурата

на клетката

изолационният

слой,

плаващият

гейт и управляващият

гейт са общи.

Най-интересното

тук е общият

плаващ гейт,

който е

изпълнен като

тънък слой

силициев

нитрид (Si3N4) .

Уникалното

на този

материал е

това, че той не

позволява

разсейването

(протичането)

на натрупания

заряд като го

удържа

компактно локализиран

в областта на

съответния

дрейн, от

който е

създаден.

Така тази

конструкция

позволява

съхраняването

в двата края

на два

информационни

бита. При

запис в плаващия

гейт се

инжектират

горещи

електрони, а при

изтриване –

дупки, които

неутрализират

отрицателния

заряд.

Фиг. 4.2.3.11. Структура

на NROM-клетка

Има

разбира се и

други

конструкции,

като например

Stacked Gate Cell (клетка с

многослоен

гейт), SuperFlash Split-Gate (клетка

с разцепен

гейт), Two Transistor Thin Oxide Cell (Дву-транзисторна

клетка с

тънък слой

оксид) и др..

Основните

недостатъци

на

MLC-структурите

са:

·

Понижена

надеждност в

сравнение с

SLC-структурата.

Това налага

вграждането

на по-сложен

механизъм за

корекция на

грешките

(колкото

повече битове

се падат на

една клетка –

толкова

по-сложен е

този

механизъм);

·

MLC схемите

обикновено

имат по-ниско

бързодействие;

·

Въпреки

че размерите

на двата типа

клетки са

почти

еднакви, в

MLC-схемите се

отделя допълнително

място за

специфичните

схеми за

четене и запис.

Ресурсът за многократен запис на данни във флаш паметите също следва да се познават добре. Промяната на заряда в плаващия гейт е съпроводено с необратими изменения в неговата структура. По тази причина броят на записванията е ограничено (от 10.000 за SLC, до 100.000 за MLC). Една от причините за деградацията, това е невъзможността индивидуално да се контролира заряда в плаващия гейт на всяка отделна клетка. Проблемът е в това, че запис и изтриване се изпълнява върху множество клетки едновременно (неотменимо свойство на флаш паметта). Автоматът за запис контролира достатъчността на инжекцията на електронния зарад, използвайки референтна клетка или по средната му стойност. Но постепенно зарядите в отделните клетки се разсъгласуват и в определен момент е възможно някой от зарядите да излезе от допустимите граници, които автоматът за запис може да компенсира чрез инжекция (или да възприеме автоматът за четене). Ясно е че този ресурс се влияе от идентичността на клетките. За съжаление със снижаване на дискрета на технологиите последните все повече се затрудняват в осигуряването на идентичността, ето защо ресурсът на запис става все по-трудно да се увеличава. Друга причина влияеща на ресурса за запис това е взаимната дифузия на атомите от изолиращите и проводящите области в общата полупроводникова структура. Дифузията се ускорява от градиента на електрическото поле в областта на канала и от множеството пробивания на изолатора при запис и изтриване. Всичко това води до размиване на границите и влошаване на качеството на изолационния слой, което пък причинява скъсяване на времето за съхранение на заряда.

Срокът

за

съхранение

на

информацията

също е важен

параметър.

Изолацията

на плаващия

гейт не е

идеална и с

времето се

променя.

Срокът за

достоверно

съхранение

на данните

според

повечето

производители

се определя

до 15-20 години. На

тази

характеристика

силно влияят

външните

условия –

повишена

работна

температура

или пък

различни видове

радиационно

облъчване.

Честотата и броят

на четенията

на данните

също са

причина за “износване”

и за

възникване

на грешки.

Йерархическа

структура.

Изтриването,

записът и

четенето на

флаш паметта

винаги

протича

върху

относително

големи

блокове. За

различните

памети обемът

на блока

варира -

размерът на

блока при

изтриване е

винаги е

по-голям от

този при

запис, при

това

размерът на блока

при запис е

не по-малък

от размера на

блока при

четене. Така

като

следствие

всички

интегрални

схеми на флаш

паметите

имат йерархическа

структура -

паметта е

разбита на

блокове,

блоковете се

състоят от

сектори, а

секторите от

страници. В

зависимост

от

предназначението

на

конкретната

схема дълбочината

на йерархия

както

размерът на елементите

се променя.

Например,

NAND-схема може

да има размер

на блока при

изтриване стотици

[KiB], при размер

на

страницата

за запис и четене

4[KiB]. За NOR-схеми

блокът за

изтриване

може да има

размер до

стотици [KiB],

размерът на

сектора за

запис – до

стотици [B], а

размерът на

страниците

за четене – до

няколко

десетки байта

[B].

Обем

на флаш

схемите.

Намаляването

на

производствения

технологичен

дискрет

способства

за бързото

увеличаване

на обема на

интегралните

схеми. През 2000 г.

дискретът е

бил 180[nm], което

води обем от

512[Mib]. През 2005 г.

дискретът е 90[nm],

който позволява

обем на

схемите 2[Gib].

След това се

преминава

към схеми с

MLC-структурата

и в 2008 г. при

дискрет от 65[nm]

обемът е вече

8[Gib]. През 2010 г. се

достига до 16[Gib],

а през 2014 г. – до 64[Gib]

при

технологии с

дискрет под 20[nm].

През 2018 г.

производителите

използват

технологии с

дискрет от 12[nm] с

тенденции

през 2019 г. той да

бъде намален

до 10[nm]. При тези

размери,

заедно с

останалите

архитектури

решения,

обемът на

флаш схемите

достига впечатляващите

размери от 512[Gib]

до 8[Tib]. Това пък

води до невероятно

разширяване

на областите

за приложения

и

производството

на нови

високо технологични

изделия.

Архитектури

на флаш

паметта

Архитектура NOR

За

автор на NOR

архитектурата

се приема

форма Intel.

Организацията

на NOR флаш

паметта е

идентична с

тази на динамичната

памет.

Запомнящите

елементи (MOS транзистори

с плаващ

гейт) са

подредени

матрично (по

редове и по

колони),

оформяйки по

този начин

отделните

запомнящи

клетки и блокове,

както и общия

обем на

паметта.

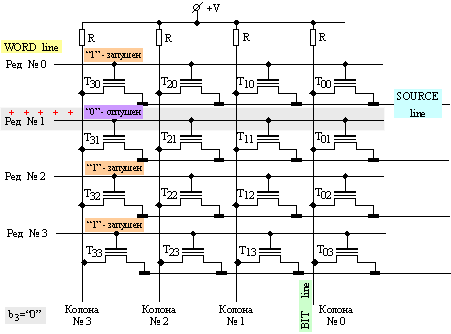

По-долу е

показан

запомнящ

масив с

организация

3х4х1.

Запомнящите

елементи се

управляват по

трите

електрода,

означени в

долната рисунка

като word line, source line и bit

line. Един от

електродите

на

запомнящия

елемент (сорс)

е свързан към

общата маса (source

line), а другият (drain)

е свързан към

съответния

битов

проводник (bit line).

Тъй като

всички

запомнящи

елементи в

дадена

клетка

следва да са

достъпни за

операция

четене или

запис едновременно,

то техните

управляващи

електроди

(гейтовете)

са свързани с

общ

проводник (word line).

Този

проводник

може да се

приеме за адресен,

тъй като е

единствен за

дадената

клетка.

Фиг. 4.2.3.12. Запомняща

матрица на NOR

флаш памет

Така за получаване на достъп до клетка от паметта е необходимо да се подаде положително напрежение на адресната й линия (word line), т.е. на управляващия гейт на всички транзистори в съответния ред, например на средния ред (ред №1) в горната рисунка. Колко бита 8,16,32 или повече се четат успоредно, зависи от ширината на данновата шина на паметта.

Съдържанието

на всеки

отделен бит

на така

адресираната

клетка се

определя

според

нивото на

сигнала, снет

от линията на

съответната

колонка (bit line),

свързваща дрейна

на всички

транзистори

в колонката.

Сорсовете на

транзисторите

в избрания

ред в този момент

са свързани

към маса.

Името си

паметта

дължи на логическата

операция

ИЛИ-НЕ (NOR). Тази

операция получава

логическа

стойност

единица само

в случай, че

всички нейни

операнди са

нули. Във

всички

останали

случаи

резултатът е

единица. Ако

в случая под

операнд

разбираме

значението

на

напрежението

в точката на дрейна

на

транзисторите,

то на

съответната

даннова

линия

(колонка) ще

има единица,

само ако

всички

транзистори

в колонката

са запушени.

За пример на

фигура 4.2.3.12 сме

показали

избора на ред

№1. В резултат

на положителното

напрежение

на гейтовете

на транзисторите

в този ред,

същите

стават достъпни.

Последното

означава, че

окончателното

им състояние

е зависимо и

се определя

от количеството

електричество,

акумулирано в

техните

плаващи

гейтове. Така

някои от тях

ще се отпушат

напълно, а

други ще

останат в

запушено

състояние. По

този начин на

данновите линии

(колонки №0, 1, 2 и 3)

възниква

(прочита се)

запомнената

върху всеки

отделен

плаващ гейт логическа

стойност. За

надеждо

прочитане на

логическото

ниво всяка

даннова линия

е осигурена с

усилвател и

формировател.

Вертикалната

връзка, която

обединява дрейновете

на

транзисторите,

заедно с активното

съпротивление

R, както и

самите транзистори,

образува

логическата

функция ИЛИ.

Тук

читателят

трябва да си

припомни

функцията на

опроводените

в обща точка

дрейнове (в

случая), за

която сме

писали на

много места в

нашите книги.

И тъй като

останалите

редове, т.е.

клетки, не са

избрани,

логическата

стойност,

която се

чете,

например, от

линия №1, точно

съответства

на

съхраняваната

в избрания

транзистор Т31

логическа

стойност. Ако

приемем, че

транзистор Т31

се окаже

отпушен, то

бит b[3] ще се

прочете като нула.

Така

резултатът

върху

данновата

линия №3 е:

![]()

В този тип флаш памет достъпът до клетка и прочитането на нейното съдържание е много бърз процес (всички битове се прочитат едновременно, паралелно). Процесите на запис и на изтриване обаче са доста по-бавни. Освен това за флаш паметите съществува проблема с мащабируемостта. Същността на този проблем се състои в невъзможността да бъде намалена площта на интегралната схема чрез намаляване на площта на запомнящите елементи, към всеки един от които следва да се подведе индивидуален контакт.

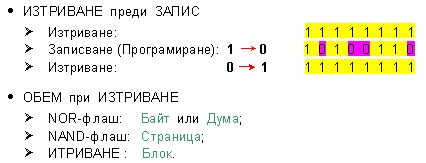

Първоначалното състояние на NOR клетка е еквивалентно на логическа единица “1”, защото токът ще протича през канала при подаване на подходящото напрежение към управляващата (адресната) линия. Така се формира напрежението на битовата линия.

Запис на нула (0) в даден запомнящ елемент се осъществява чрез едновременно подаване на положително напрежение на адресната линия (word line) и високо положително напрежение на данновата линия през съпротивлението R, с което се осигурява отрицателна потенциална разлика между гейта и сорса (вижте фигура 4.2.3.8 и обясненията към нея). В резултат на това от плаващия гейт се изсмукват носителите на електричество, които тунелират обратно към истока (дрейна). Така, когато този транзистор бъде избран, той ще бъде отпушен. На контролерът на паметта при програмиране и при изтриване е възможно да му се наложи да изпрати няколко импулса към клетката до постигане на правилното ниво. При изтриване всички клетки в един блок (сектор) на паметта се изтриват едновременно. Операция четене от NOR-флаш памет е подобно на четене от адресируема RAM-памет, стига дължината на адреса и порцията данни да са съгласувани. При тези условия процесорът може да изпълнява програмен код, четейки го директно от флаш паметта, без преди това да го прехвърля в RAM-паметта. Програмирането (записът) на NOR клетки обикновено се изпълнява върху актуалната даннова дължина на порцията (байт или дума).

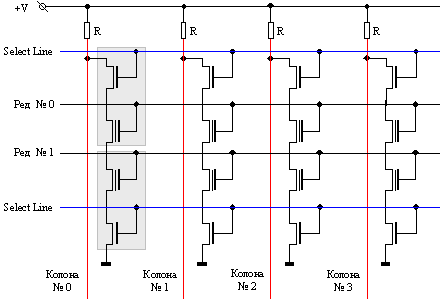

Архитектура NAND

Архитектурата NAND, за автор на която се счита фирма Toshiba, може да се представи както е показано на долната фигура 4.2.3.13. Тя съответства по аналогичен начин на логическата операция И-НЕ (NAND). Тази операция дава нулева логическа стойност (“0”) само ако всички нейни операнди са равни на единица (“1”) . Във всички останали случаи (при поне една нула) резултатът е логическа единица. Този ефект се дължи на последователното включване на транзисторите. Единият край на последователно включените транзистори е подключен към маса, а другият е подключен към данновата линия. Запомнящите клетки са подключени в групи по 16. Тези групи са обединени в страници, а страниците – в блокове. При тази структура на запомнящия масив обръщението към отделна клетка е невъзможно. Записването се изпълнява в пределите на една цяла страница, а при изтриване обръщението е към цял блок или група блокове.

Фиг. 4.2.3.13. Запомняща

матрица на NAND

флаш памет

Както вече отбелязахме логическата нула (“0”) съответства на отпушен транзистор, затова данновата линия в NAND архитектурата подава нулева стойност само в случая когато всички подключени към нея транзистори са отпушени и единична стойност – когато поне един от транзисторите е запушен. Характерно за флаш паметта са следните действия:

Получаването на такива резултати се постигат ако транзисторите са подключени към данновата линия не по отделно (както е в архитектурата NOR), а в последователни серии (по няколко на една линия), както е изобразено по-горе на фигура 4.2.3.13. Тази организация е предразположена към последователен интерфейс. Следващата фигура илюстрира вътрешната структура на ядрото на паметта.

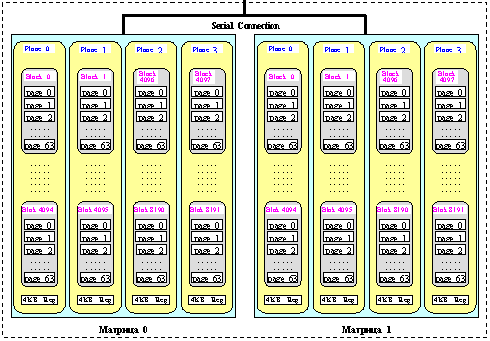

Фиг. 4.2.3.14. 2[Gib] Micron -

организация

на ядрото на NAND

флаш памет

Всяка интегрална схема може да пакетира множество ядра. Всяка секция (равнина) има собствен регистър за страници и кеш-регистър. Страниците на отделните матрици могат да се четат или програмират едновременно. Матриците се опаковат с по 1, 2, 4, 8, ... ядра.

Фиг. 4.2.3.15. Флаш

опаковка с

обем 4[GiB]

Читателят може да получи значително по-подробна информация за строежа на флаш паметите от фирмените и от научните публикации, пример за което е следната:

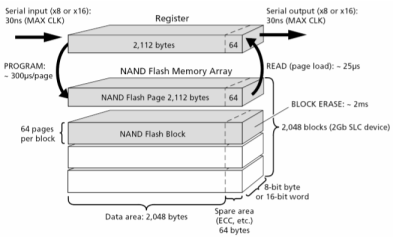

NAND Flash Memory Organization and Operations

Изтриване на данни става само по цели блокове. Страниците са обикновено на брой 512, 2048 или 4096[B]. Няколко байта (обикновено 1/32 от размера на данните) са свързани с всяка отделна страница и са предназначени да съхраняват кода на контролната сума (Error Correcting Code - ECC), чрез която данните могат да бъдат поправени, ако в тях настъпи грешка. Размерите на блоковете най-често са:

· 16[KiB], който съдържа 32 страници, всяка от които с обем от 512[B] + 16[B] ;

· 128[KiB], съдържащ 64 страници, всяка от които с обем от 2048[B] + 64[B] ;

· 256[KiB], съдържащ 64 страници, всяка от които с обем от 4096[B] + 128[B] ;

· 512[KiB], съдържащ 128 страници, всяка от които с обем от 4096[B] + 128[B] ;

Всяка страница, освен потребителска информация, съхранява и служебна такава. Последната се отнася до това дали тя е “лоша" и какъв е кода за корекция на грешките ЕСС. NAND флаш паметите използват ЕСС-код за откриване и поправяне на еднобитови грешки в данните с достатъчна дължина. Например, 22[b] са достатъчни за данните, съдържащи се в една страница с обем 2048[b]. За страници с обем от 4096[b] ЕСС-кода има дължина 24[b]. Ако е необходимо да се промени (да се поправи) съдържанието на даден бит в тази лоша страница, то след процедурата за поправка на грешката, цялата страница се презаписва. Ако контролерът не успее да поправи грешките в даден блок, той се маркира като “лош”. Възможна е и процедура по подмяна на лош блок с добър. За целта съществува допълнителен регистър, в който първоначално се копира съответният блок. След това в регистъра се извършва поправка на данните, а данните в изходния блок се изтрива. Едва след това данните от регистъра се връщат в изходния блок.

Потребителят не бива да разчита на максималния обем на паметта, деклариран за дадената интегрална схема. Тъй като при производството на интегрални схеми степента на годност не е 100%, а да се бракуват памети, в които има 1 или 2 лоши блокове е неприемлива практика, още с доставката схемите могат да съдържат блокове, които са вече маркирани като лоши, в резултат на което полезният обем е занижен (незначително). Поради споменатите недостатъци не се препоръчва директното изпълнение на програмен код, намиращ се в NAND-флаш памет. Тъй като данните в този тип памет могат да се преместват (в следствие на подмяната на лоши с добри блокове), NAND-флаш паметта следва да се използва в системи с виртуално адресиране (за това ще говорим в глава 6 на тази книга). За по-висока надеждност програмният код се изпълнява след прехвърляне в RAM памет.

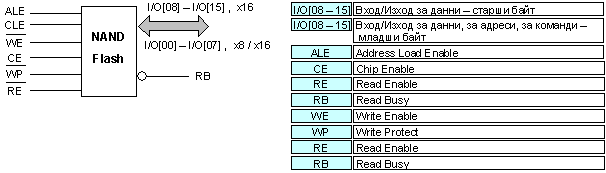

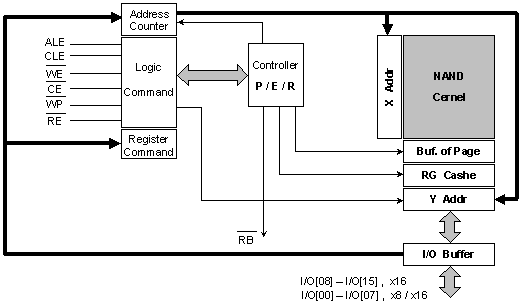

Ще поясним кратко примерната логическата структура на завършена интегрална схема. Схемата има обща мултиплексируема входно-изходна и адресно-даннова шина, ширината на която варира (8[b] или 16[16]).

4.2.3.16. Примерна

логическа

структура на

NAND флаш памет

Производствената технология на тази памет постига по-добра мащабируемост. За разлика от предидущата памет тук при запис се използва методът на тунелиране, с който се постига по-бърз запис. За да се компенсира ниската скорост при четене, в интегралните схеми с NAND архитектура изграждат допълнителна буферна (кеш) памет. Освен разгледаните архитектури съществуват и други.

Интегралните

схеми на флаш

паметите

имат удобен

интерфейс и в

много случаи

добре се съчетават

със

стандартните

сигнали, използвани

в

микропроцесорните

системи.

Както и динамичните

памети, флаш

паметите се

управляват

чрез

собствени

команди,

които

представлява

определени

комбинации

от стойностите

на

собствените

им

управляващи

сигнали. Въпреки

че тези

памети се

отнасят към

паметите с произволен

метод за

достъп,

изпълнението

на основните

операции (в

смисъла,

който вложихме

в това

определение

за

операциите,

възможни за

изпълнение в

адресируемите

памети), тук

тяхното

изпълнение е

свързано с

особени и

различни

алгоритми,

наложени от

принципите

за работа на

запомнящите

елементи и

принципите

за

организация

на

запомнящите

масиви. Тези

алгоритми са

заложени във

вътрешните

управляващи

флаш паметта

автомати, така

че когато

външно се

заповяда

операция

четене, тя

всъщност се

изпълнява

вътрешно

според

съответния

алгоритъм.

Освен това

флаш паметите

изпълняват

допълнителни

специфични

операции,

които са

осигурени с

особени сигнални

микрокоманди.

Ще

представим

само списък

на тези

команди за

флаш памети

второ

поколение на Intel:

·

Read Array/Reset – четене

на

запомнящия

масив;

·

Read ID – четене на

идентификатора

на

производителя

и на

устройството;

·

Read Status Register – четене

на

съдържанието

на регистъра

на състоянието;

·

Clear Status Register –

изтриване на

съдържанието

на регистъра

на

състоянието;

·

Erase Setup/Erase Confirm –

изтриване на

съдържанието

на блок;

·

Erase Suspend/Erase Resume –

временно

спиране на

операция

изтриване с цел

четене на

друг блок;

·

Program Setup/Program –

подготовка и

програмиране

на клетка.

Високите

напрежение и

ток

представляват

съществен

недостатък

на

флаш-технологията.

Допълнителен

проблем се

появява от

прекомерното

изтъняване

на

изолационния

слой. При дебелина

под 90[nm] започва

дрейф на

носители

през изолатора,

което прави

невъзстановима

записаната

информация.

При ниво на

детайлизация

под 65 [nm]

влиянието на

заряда в

плаващия

гейт върху

останалите

елементи

става

значително,

което пречи

на процесите

на запис.

Това ниво на

детайлизация,

което се

счита че ще бъде

масово

усвоено към 2007

година се

приема за

сега като

предел във

възможностите

на

флаш-технологиите.

Разработването

на различни

конструкции

на флаш

елемента продължава.

Въпреки това

много

специалисти

не вярват в

перспективността

на съвременните

флаш

технологии

поради

съществените

проблеми в

минитюаризацията

и увеличаването

на скоростите

на

функциониране.

Определено

се считат, че

флаш

технологиите

най-вероятно

ще бъдат

заменени от

усилено

развиващите

се в момента

технологии

на базата на

фероелектрическия

принцип за

съхраняване

на информация

(Ferroelectric RAM).

Енергонезависимата

FeRAM памет има

елемент с

проста

структура,

висока

скорост и

надеждност

при

експлоатация.

Тази памет е

устойчива на

различни

излъчвания

включително

и на

радиация.

В

настоящия

момент почти

всички

видове външни

флаш памети

използват

или USB, или АТА/SATA

интерфейс.

Тъй като този

интерфейс

никога не е бил

предвиждан

за

комбиниране

със скоростта,

предлагана

от флаш

паметите,

скороста, която

той може да

постигне, е

значително

по-ниска от

максимална

за тях на

теория. Дори USB

2.0, увеличаващ

значително

скоростта на

трансфер в

сравнение с

първото

поколение USB,

не може да

достави

необходимата

пропускателна

способност.

Пътищата за

промяна са

два –

цялостна

преработка

на

архитектурата,

с използване

на подобрени

производствени

технологии,

или на

интерфейса, с

който устройството

комуникира

със

системата.

Към 2019 година

скоростта за

трансфер при

SSD дискове с

интерфейс USB 3.1

надхвърля 500[MiB/s].

Докато

първата

възможност е

доста скъпа за

въвеждане, то

промяната на

интерфейса

може да

доведе до

значителен

скок в производителността

на флаш

паметите. За

целта Intel

предлага

разработката

на Open NAND Flash Interface (ONFI),

представляващ

специализиран

интерфейс за

връзка между

флаш памет и

компютърната

система. В ONFI Intel

използва

методи,

намиращи

приложение в

DDR SDRAM паметите,

HyperTransport, PCI-Express и т.н. –

това са source synchronous data strobes

и DDR трансфери.

Първото от

двете

представлява

схема, при

която

контролерът

синхронизира

изпращаните

данните. Така

се постига гъвкавост

в скоростта

на трансфер,

независеща

от общ

генератор на

сигнали.

Според проектите

за

разработване

на ONFI на Intel,

първото

поколение ще

предлага

скорост на трансфер

от порядъка

на 40 [МВ/s],

второто – над 133

[МВ/s], а третото –

266 [МВ/s]. До

момента

реално е

завършена

само

спецификацията

на първото

поколение ONFI.

Тя е свободно

достъпна на

сайта на

организацията,

занимаваща

се с нейната

разработка.

Впрочем

идеята за ONFI се

развива не

само от Intel, но

и от още

няколко

големи фирми

– Hynix, Micron Technology, Phison, Sony, STMicroelectronics и

др.

Следващо

поколение в

архитектурите

на флаш

паметта. 3D NAND

В

съвременни

условия вече

сме

свидетели на

бързи,

безшумни и

безгрешни

дискове, известни

като

SSD-дискове (Solid State Drive). За тези

дискови

устройства

читателят

може да чете

на следния

адрес:

Същността

на SSD се

изгражда от

флаш памети с

големи обеми,

което

позволява на

дисковете да

надминат

обеми в

дименсията

терабайт [TiB], с

тенденция за

непрекъснато

увеличаване.

Постигането

на тези

огромни

обеми се дължи

най-вече на

нови

архитектурни

решения в

конструкцията

на флаш

паметите.

Наименованието

на новата

архитектура

е 3D Xpoint, но то се

налага

частично. Технологията

е обявена за

първи път от Samsung

в края на 2013

година,

когато

фирмата

достига

капацитет на

паметта от 128[Gib] за

един чип.

През 2015 г.

обемът

достигна до

256[Gib], а през 2017 г. – до

512[Gib]. Веднага

след това в

разработка

на тази архитектура

се включват

още Intel и Micron,

които

обявяват

своя краен

резултат

през 2015 година

под името 3D NAND.

Когато през 2015

година технологичният

дискрет

достига 15[nm],

става ясно,

че пътят на

“екстензивното”

развитие на

еднослойните

технологии е

вече

извървян.

Преходът на технологиите

към по-малък

дискрет (13[nm] и

по-надолу до

10[nm]) води до

увеличена

вероятност

за свободно

изтичане на

електрони

между

отделните

клетки,

особено в тези,

със

структура MLC и

TLC), което води

към следващи

архитектурни

разработки.

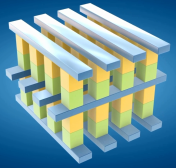

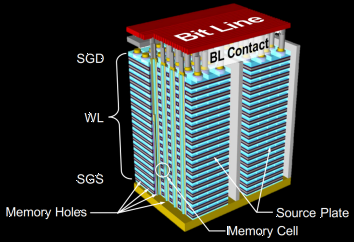

Обемната, непланарна 3D NAND флаш е такава памет, в която планарните секции с равнинно матрично разположените клетки са мултиплицирани многократно. Така изградените секции (вижте фигура 4.2.3.15) са подредени вертикално, една върху друга, образувайки при това една многослойна (кубическа) формация. Броят на обявените през 2019 година слоеве в кубическата структура е достигнал числото 128. Следващата рисунка илюстрира вертикалното разположение на запомнящите клетки.

4.2.3.17. Същност

на логическа

структура на

3D NAND флаш памет

Всяка запомняща клетка в тези структури е от тип TLC, което позволява висока плътност на съхранение при по-ниска цена за един бит. Както вече писахме в началото на този раздел, TLC клетката има общо осем възможни състояния: 000, 001, 010, 011, 100, 101, 110 или 111. Последните се различават с помощта на прецизно управление на напрежението, снемано от управляващия гейт.

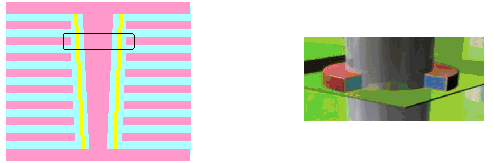

Производствените

технологии

на 3D структурата

са различни и

не всички са

били успешни.

Тук ние няма

да ги

описваме

подробно, но

не можем да

ги оставим

без никакво

внимание. Кратко

ще поясним

същността на

технологията

на Samsung, при

която се

използват

транзистори

с плаващ

гейт, имащ

особена

(цилиндрична)

форма,

определяна

като Charge

Trap Flash

(капан за

заряда). Върху

кристалната

подложка

последователно

един върху

друг се

наслояват

проводящи и

изолационни

слоеве. В

последствие,

в дълбочина,

през тези

слоеве, в две

направления,

формират множество

отвори.

Следващата

рисунка

показва

такава

примерна

8-слойна

конструкция.

С червен цвят

са означени

проводящите

области, а

със син

изолиращите.

Плаващият

гейт се представя

от жълтия

цилиндър, а

оградената с черно

част от

конструкцията

включва цилиндричния

транзистор,

показан в

дясната част

на фигурата.

4.2.3.18. Цилиндрична

3D структура

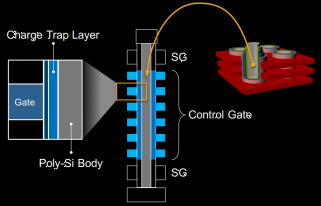

След това вътрешната повърхност на всеки отвор получава множество покрития: първо силициев диоксид (изолиращ), след това силициев нитрид (проводящ), след това втори слой силициев диоксид (изолиращ). Накрая, дупката се запълва с провеждащ (легиран) полисиликон. Така върху повърхността на стените на цилиндричните отвори е нанесена структурата на полевите транзистори - изолатори и плаващи гейтове. По този начин се формира всеки стълб от кръгообразните полеви транзистори. Това дава основание на някои фирми да определят тази памет като вертикална – V NAND Flash. Интегрална схема V NAND с обем 128[Gib], имаща 24 слоя, изисква около 2,9 милиарда такива дупки, а както споменахме, последното съобщение за броя на слоевете е за 128.

Следващата

фигура

отново

илюстрира

цилиндричната

V NAND структура.

4.2.3.19. Цилиндрична

3D структура

Производствената технология за изграждане на кратко описаната обемна структура включва изключително сложни и специално разработени процеси, които няма да поясняваме подробно. Те са същност на съвършено друго научно-техническо направление. Тук ние няма да се потопяваме в дълбочина при изясняване на същността на най-новите технически решения - не това е нашата цел. Отново ще упътим читателя към научните публикации, като например:

3D NAND Flash Based on Planar Cells

За задълбочено изучаване на този вид памети препоръчваме на читателя книгата

3D

Flash Memories, Rino Micheloni, Springer - 2016, ISBN 978-94-017-7510-6,

380 pages.

Тук, след като изложихме достатъчно подробно основните принципи за реализация и организация на флаш паметта, нейно по-нататъшно изучаване считаме, че трябва да бъде самостоятелна задача на читателя.

Следващият

раздел е:

§ 4.3

Логическа

структура на

запомнящи устройства

с

последователен

достъп