Последната

актуализация на този раздел е от 2020 година.

5.4.1 Видове прекъсвания и условия за обслужване

Ще продължим да разглеждаме случайните заявки за прекъсване, предвид на това, че тяхното обслужване е най-трудното за организиране. Освен определените по-горе времеви характеристики (параметри), системата за прекъсване на даден процесор се характеризира и с някои допълнителни параметри. Вече беше казано, че входът за постъпване на заявки за прекъсване непосредствено в процесора е само един. Той е един, защото от гледна точка на първичния организационен алгоритъм – командния цикъл, един е напълно достатъчен. Практиката обаче показва, че процесорът трябва да “общува” с твърде богато по състав и характер външно обкръжение, защото заедно с него той може да изгради една практически полезна и приложима компютърна система. Ето защо е важно да се знае какъв е общият брой възможни за подаване заявки за прекъсване и какво е тяхното отношение спрямо изчислителния процес. Можем да твърдим, че колкото той е по-голям, толкова по-гъвкава и развита може да бъде периферната система на процесора. Още тук в началото искаме да предупредим читателя, че обясненията понякога изискват посочване на реални примери. С това се цели обосноваване на едно или друго съответно обобщение. Моделите процесори са много и всеки един предлага своите конкретни реализации, които разбира се, тук не е възможно да разгледаме. Темата обаче е толкова фундаментална, че каквито и реализации, настоящи или бъдещи, читателят да срещне, изложеното тук е принципно общовалидно.

Друга

характеристика на системата за прекъсване е максимално възможната дълбочина на вложените прекъсвания, която тя може да поддържа. С други думи, това е максималният брой

програми, които могат да стоят прекъснати, без да е загубена възможността да

бъдат завършени. Ако например след прехода към обслужващата програма и по време

на нейното цялостно изпълнение, приемането на други ЗП е забранено, това

определя дълбочината на единица. Дълбочината е цялото число N, ако е възможно да бъдат

взаимно прекъснати N на брой програми.

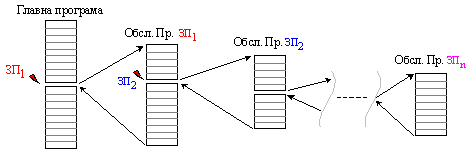

Фиг. 5.4.1.1. Схема на последователно вложени

прекъсвания

Горната фигура илюстрира схемата

на влагане на програмни единици при последователно обслужване на заявките за

прекъсване. Схемата е аналогична на тази от фигура

2.1.4, изразяваща програмни прекъсвания при преход към подпрограми.

Принципното отличие в разглежданата тук ситуация се състои в самата външна

причина и нейния случаен характер.

Заедно с

извънредните ситуации, които могат да възникнат и да поискат вниманието на

процесора, той самият е полезно да може да превключва своето внимание към

различните видове дейности, изпълняващи се паралелно в него самия и в средата

на неговото обкръжение. Тъй като общото управление на компютърната система се

осъществява по програмен път, то този вид прекъсвания следва да се генерира по

програмен път. Така в този смисъл различните прекъсвания могат да бъдат

разделени на две групи:

1.

Вътрешни прекъсвания (програмни

и апаратни) ;

2.

Външни прекъсвания.

Според

вероятните за поява причини, заявките за прекъсване се класифицират в три

основни групи:

1.

Външни прекъсвания:

·

От периферни устройства, изискващи обслужване;

·

От таймер;

2.

Аварийни прекъсвания:

·

Поради грешки при изпълнение на програмите - при

несъществуващ КОП, при аритметични операции, при обръщение към паметта, при

защита на операционната система ;

·

От диагностичната система - при

загуба на информация в предаваните данни, при отпадане на захранването, при

нарушаване на работните условия на отделни ИС ;

3.

Програмни прекъсвания – при

преход към подпрограма или към процедура, при преход към друго задание

(процес), при връщане от прекъсване.

Според

изискванията си за обслужване, прекъсванията могат да се класифицират в две

групи:

1.

Прекъсвания, които изискват безусловно обслужване ;

2.

Прекъсвания, които се обслужват при определени условия.

Прекъсванията

от втората група се характеризират с това, че тяхното обслужване може да бъде

отложено, или забавено, докато настъпят благоприятни за това условия. Обикновено

задържането, или блокирането на обслужването, се управлява от програмиста чрез

предварително програмно установени условия, наричани маски на заявките за прекъсване.

Така тези прекъсвания, обслужването на които се влияе от стойността на маските,

са получили наименованието маскируеми.

Добре е маскируемите прекъсвания да постъпват на отделен вход – вход за маскируеми заявки.

Прекъсванията

от първата група изискват безусловно обслужване и като алтернативни на

предидущите се наричат немаскируеми, т.е. тяхното обслужване не може

да бъде отлагано или задържано с програмни средства. Тези заявки се приемат на

отделен вход - вход за немаскируеми заявки.

Така в

процесорите, непосредствено към централното управляващо устройство, се налага

реализация на един вход за външни маскируеми прекъсвания, означаван обикновено

с мнемониката INT (Interrupt) или IRQ (Interrupt request) и един вход за външни немаскируеми прекъсвания, означаван с мнемониката

NMI (Non-maskable Interrupt).

Немаскируемите прекъсвания (NMI) се използват за сигнализиране за фатални апаратни

грешки. На заявките за този вид прекъсване процесорът реагира винаги

(ако е завършено обслужването на предидущото немаскируемо прекъсване). На този

вид прекъсване съответства фиксиран вектор - №2. Сигнал на вход NMI в процесора идва от контролера на паметта, или от контролерите на

системните шини. Другото немаскируемото прекъсване - SMI (System Management

Interrupt) може да се яви когато процесорът работи в режим на системно

управление (SMM – System Management Mode). Източник на това немаскируемо

прекъсване могат да бъдат схеми от чипсета на системата, които участват в

управлението на енергийното потребление, а така също от USB-контролера (при

подключване на клавиатури или мишки). Режимът на системно управление SMM е предназначен

за изпълнение на операции прозрачно от програмното осигуряване и дори от

операционната система. При този режим се реализира конкретна функция от

системата за сигурност на процесора и/или от системата за обслужване на

консумацията. Няма програмна възможност за преминаване в SMM. Преходът в този

режим е единствено апаратен по ниско ниво на входа за прекъсване SMI. Това

прекъсване се обработва от контролера на прекъсванията. Обработването на SMI

води до превключване на процесора в режим на системно управление. Когато

процесорът премине в SMM-режим, той издава сигнал

SMIACT, който служи за включване на специална област от физическата памет,

наречена System Management RAM (SMRAM). По този начин SMRAM-паметта е

достъпна само в този режим и до нея нямат достъп операционната система и

приложенията. При преминаване в режим SMM процесорът запазва по адрес SMM-Base

от SMRAM своето съдържание (по подразбиране SMM-Base е 30000h). След

това управлението се предава на процедура за обслужване на това прекъсване. Тази

процедура се намира на адрес (SMM-Base+8000h). В SMM-режим не е

предвидена работа с прекъсвания и особени случаи. Прекъсванията по линии SMI и

IRQ са маскирани, трасирането и точките на прекъсване са забранени, а

обработката на немаскируемите прекъсвания по линия NMI се обработват след

излизане от режим SMM. Процесорът излиза от SMM-режим и се връща в режима на

работа, в който е получен сигнал SMI, чрез команда RSM. Тази команда е

последна в процедурата за обслужване на прекъсването SMI. Командата RSM се разпознава само в този режим, а

в останалите режими на работа предизвиква грешка (недействителен код на

операция). С развитието на процесорите, както и в новите модели, казаното току

що може да се отличава, ето защо читателят следва да се запознава самостоятелно

с конкретния процесор.

Маскируемите

прекъсвания имат за цел да сигнализират процесора за различните събития,

настъпили в обкръжаващите го устройства. Реакцията на процесора на този вид

заявки за прекъсване може да бъде задържана (препятствана или отложена) с

помощта на вътрешната маска IF (IF=0). Установяване на маската (IF=0) се постига с

машинната команда CLI,

а свалянето ѝ (IF=1) се постига с командата STI. При възникване на събитие, което изисква специалното внимание

(обслужване) от страна на процесора, контролерът на съответното устройство

формира сигнал заявка за прекъсване. Този сигнал (заявка) по специална

линия постъпва на вход на контролера за прекъсвания APIC (Advanced

Peripheral Interrupt Controller). Задачата на последния,

събирайки всички подобни заявки, е да избере една, да я идентифицира, след

което да уведоми процесора, към който в подходящ диалог изпраща така

подготвената информация. Процесорът от своя страна решава дали да прекъсне

изпълнението на текущата програма и ако се налага преминава към друга

(специализирана) програма, чрез която ще обслужи приетата заявка за прекъсване.

След

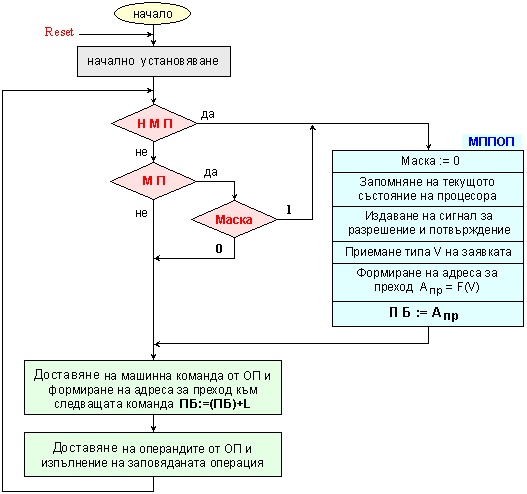

изказаните по-горе подробности, изпълняваните микрооперации в командния цикъл и

в процедурата МППОП при анализ на заявките за прекъсване, могат да бъдат

конкретизирани върху блок-схемата, с която той беше дефиниран (фигура 5.1.4), така:

Фиг. 5.4.1.2. Команден цикъл и МППОП

Представената блок-схема е една

стъпка в посока конкретизация на командния цикъл. Онова, което читателят трябва

да забележи в блок-схемата е, че в микропрограмната процедура за осъществяване

на прекъсването МППОП се предполага известен диалог между процесора и

външните устройства. В този диалог присъстват нови понятия, които допълнително

ще поясним. Освен това, искаме да обърнем внимание на читателя, че след

приемане на ЗП, в началото на МППОП, маската получава стойност нула. Това

означава, че след осъществяване на прекъсването и изпълнение на първата команда

от програмата за обслужване, маската е нулирана и други заявки за маскируеми

прекъсвания не могат да бъдат приемани (става дума за входа на процесора за

този вид заявки). Обслужващата програма, която се стартира по началния адрес Апр, има

своето право да остави тази маска, или да я измени, с което може да разреши

своето прекъсване. Това положение също има варианти, които ще поясним

допълнително.

От

казаното става ясно, че маската може да се управлява според нуждите на

потребителя. За целта в командната система на всеки процесор се реализират машинни команди за присвояване стойност на

маската. В командната система на процесорите Intel това са двойката безадресни команди CLI (изчистване на маската),

т.е. “забрани външни прекъсвания” и STI (установяване на маската),

т.е. “разреши външните прекъсвания”. Стойността на маската (0 или 1) се

съхранява в тригер, който обикновено е включен в състава на регистъра на

състоянието на процесора.

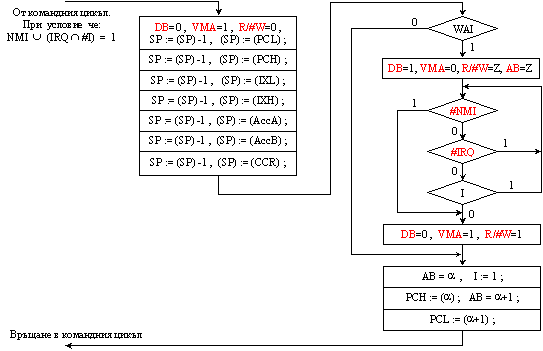

Като

конкретен пример на казаното до момента можем да предложим на читателя

блок-схемата на командния цикъл, представена на фигура

5.3.2. Там отлично се виждат микрооперациите, свързани с постъпването на

някой от външните сигнали STOP (замръзни или спри), NMI (немаскируемо

прекъсване) и IRQ (маскируемо прекъсване), както и тези, при среща

на някоя от машинните команди SWI (програмно прекъсване), WAI

(изчакай прекъсване), SEI (установи маската), CLI (изчисти

маската) или RTI (връщане от прекъсване). Микропрограмата на

команда RTI по същество възстановява съхраненото в програмния стек

състояние на процесора при последното прекъсване. Микрооперациите на тази

команда са “инверсни” на микрооперациите, които се съдържат в микропрограмната

процедура за осъществяване на прекъсването МППОП, която за дадения примерен

процесор, има следния вид:

Фиг. 5.4.1.3. МППОП на 8-битови

микропроцесори Motorola

Характерното за тази твърде елементарна 8-битова архитектура е, че адресът a, от който в края на МППОП се извлича новото съдържание на програмния брояч, се формира апаратно върху адресната шина и е константен. Стойността му зависи от вида на прекъсването. Началните адреси на обслужващите програми са постоянно записани в тези константни адреси – таблица 5.4.1.1.

Таблица 5.4.1.1 Разположение на векторите за прекъсване

|

Причина за прекъсване |

|

Физически адрес |

Начален адрес на обслужващата програма |

|

IRQ , заявка за МП |

a |

FFF8 |

Старши байт |

|

a+1 |

FFF9 |

Младши байт |

|

|

Команда SWI |

a |

FFFA |

Старши байт |

|

a+1 |

FFFB |

Младши байт |

|

|

NMI , заявка за НМП |

a |

FFFC |

Старши байт |

|

a+1 |

FFFD |

Младши байт |

|

|

Reset , сигнал за рестарт |

a |

FFFE |

Старши байт |

|

a+1 |

FFFF |

Младши байт |

Това, че архитектурата е елементарна, може

да се разбере и по това, че МППОП, която е представена по-горе, не съдържа

никакви форми за диалог с източниците на заявки за прекъсване. Нещо повече, тя,

както се вижда и от таблицата, различава само три входни сигнала, които

възприема буквално от три отделни входа (IRQ, NMI, Reset), недопускайки

възможност, за друга тяхна интерпретация. В тази крайно улеснена ситуация

началните адреси на трите обслужващи програми се намират в конструктивно

фиксирани адреси, показани в таблица 5.4.1.1, които се генерират от

управляващото устройство автоматично.

Още веднъж ще опишем текстово процеса на прекъсване, към което някои читатели са привикнали. След включване на захранването системата се конфигурира. Относно системата за прекъсване това включва инициализиране на контролера за прекъсване, назначаване на линиите за прекъсване към устройствата, установяване на указателите на процедурата за обработка. Маскируемите апаратни прекъсвания се обработват както следва:

1.

Устройството, в което възниква събитие,

формира сигнал ЗП и го подава на присвоената му линия за прекъсване ;

2.

Контролерът приема заявките от

източниците (сигнали IRQx) и при наличие на немаскирани заявки формира и изпраща към процесора

общ сигнал за прекъсване INTR ;

3.

Отчитайки наличието на сигнал за

прекъсване, ако той не е маскиран от вътрешната маска, съхранява в стека

съдържанието на регистъра на флаговете и на програмния брояч. След това

генерира сигнал за потвърждение INTA

(Interrupt Acknowledge), който е

предназначен за контролера на прекъсванията и инициира шинен цикъл за

получаване на вектора за прекъсване ;

4.

С получаване на потвърждението INTA контролерът фиксира

състоянието на своите входове. Така фиксираните заявки се подлагат на анализ с

цел избор на най-приоритетната. По време на този избор се формира и векторът на

избраната заявка, който се изпраща по данновата шина към процесора. В последствие

контролерът изпълнява и допълнителни действия в своята логическа структура,

свързани с вече изпратения вектор ;

5.

След като получи вектора на приетото

прекъсване процесорът се обръща към съответната програма за обслужване. Ако

даденият вектор се използва не само за апаратни прекъсвания, но още и за

изключение, то процедурата за обработка следва да определи типа на съответното

събитие. За това е възможно програмата да се обърне към контролера, от когото

да прочете съдържанието на регистър ISR. Това е необходимо за да анализира състоянието ;

6.

Обслужващата програма следва да

идентифицира устройството, което е генерирало ЗП. При разпределено подключване

на няколко външни устройства следва да се изпълнят няколко последователни

обръщения към всяко от последователните устройства, при което трябва да се има

предвид, че ЗП може да има от няколко устройства. Ще трябва да се направи избор

като се спази приоритета ;

7.

Програмата обслужваща даденото прекъсване

трябва да изпълни необходимите “полезни” действия за устройството, подало

съответната ЗП. При това трябва да снеме сигнала за ЗП, свързан със съответното

събитие в съответното устройство. Ако обслужването на прекъсването се забавя, в

системата е възможно да се наложи реакция на прекъсване с по-висок приоритет.

По тази причина в обслужващата програма, след критическата ѝ част, се

включва команда STI, с която се сваля маската за прекъсване IF в процесора.Така става възможно да се обслужват

вложени прекъсвания (вижте фигура 5.4.1.1

по-горе) ;

8.

Програмата за обслужване изпълнява

команда EOI (End Of Interrupt). С това се разрешава на контролера за прекъсване да приема нови заявки

както от обслуженото, така и от другите устройства. Сигнал за това се изпраща

от процесора на водещия контролер и на водените такива. Участъкът от

обслужващата програма след команда EOI, до завършващата команда IRET, се определя като критическа секция, по време на която нейното

прекъсване не е разрешено. Това изисква командата EOI да се предхожда от

команда CLI ;

9.

Обслужващата програма завършва с команда IRET, с която

процесорът се връща към изпълнението на прекъснатия поток от команди. Това се

обезпечава с извличане на съхранената преди това в стека информация.

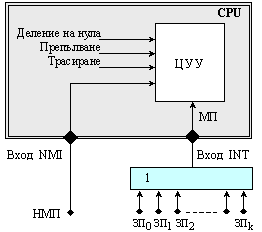

Подключването на множеството външни сигнали, пристигащи в процесора в качеството си на заявки за прекъсване, зависи от тяхната класификация (външни или вътрешни). В общия случай обаче, заявките е логично да бъдат обединени чрез логическата функция дизюнкция (ИЛИ), както е показано на фигура 5.4.1.4.

Фиг. 5.4.1.4. Включване на външни и вътрешни ЗП

Изобразените на горната фигура

външни маскируеми заявки за прекъсване (ЗП0 ¸ ЗПk),

се обединяват за подаване към единствения вход на процесора, чрез схема ИЛИ. В

общия случай процесорът не може да различи през тази схема отделните източници

на ЗП. В даден момент последните могат да бъдат няколко. Това означава, че редът

на тяхното последователно обслужване трябва да се управлява с допълнителни

външни апаратни и програмни средства. Що се отнася до немаскируемите заявки

за прекъсване, степента на тяхното значение (на техния приоритет) е

логично по-висока от тази на маскируемите, ето защо условният блок на

тяхната проверка предхожда този на маскируемите заявки, което може да се

види както на фигура 5.4.1.2 по-горе, така и на фигура

5.1.4. Вътрешните немаскируеми заявки за

прекъсване са унитарни, което означава, че редът в който те ще се обслужват е фиксиран

в управляващото устройство.

За

реализация на процедурата "осъществяване

на прекъсването" и по двата входа, илюстрирани по-горе, както и за

генериране на съответните сигнали в процесора, съществува определена логическа

схема.

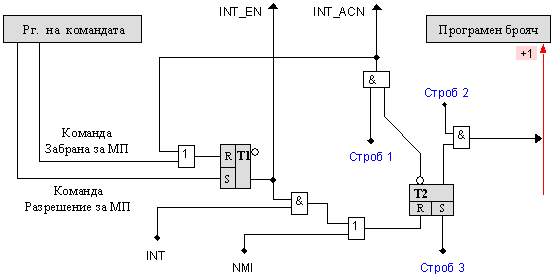

Фиг. 5.4.1.5. Вътрешна схема за прекъсване

От схемата се разбира, че

немаскируемото прекъсване NMI нулира тригера Т2, с което се преустановява изменението на

програмния брояч и се отваря единият от входовете на схемата И, формираща

потвърждението INT_ACK. Последното се издава като изходен сигнал от процесора,

когато управляващото устройство достигне до съответната микрооперация и издаде

управляващия сигнал “Строб 1”. С това се установява и маската INT_EN=0.

Ако INT_EN=1, приемането на маскируемото прекъсване по входа

INT е разрешено. С постъпване на заявка по този вход и при условие, че тригер Т1 е в единично

състояние, действието на схемата е аналогично. Показани са двата входа, с които

по програмен път се управлява стойността на маската в тригер Т1.

Привеждане на схемата в готовност за повторно прекъсване се постига чрез

управляващия сигнал “Строб 3”, който установява тригер Т2 в единично състояние.

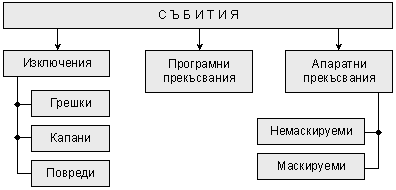

В съвременните

компютърни системи се е наложило понятието събитие.

Събитията генерално се делят на вътрешни и външни. Вътрешните събития се

наричат още изключения, а външните – прекъсвания. Тяхната йерархия може да бъде

представена по следния начин:

Фиг. 5.4.1.6. Йерархия на видовете събития

Разглеждайки конвейерната

организация ние вече казахме, че има известно разминаване между момента на

откриване и момента за реакция на случващите се при изпълнение на машинните

команди в конвейера събития. По тази причина трябва да се говори за реализация

на точно прекъсване, което ние по-късно

ще направим.

В обявената интерпретация вътрешните изключения се делят на три вида:

1.

Грешки (faults). Грешките се откриват преди или по време на изпълнението на машинната

команда. Най-често се явяват в системата на

виртуалната памет, когато от страна на процесора е заявен адрес към

несъществуваща страница или сегмент. В този смисъл изпълнението на

командата е опорочено и с нея може да се постъпи по два възможни начина – да се

рестартира или да се организира нейното продължение. Тези два метода за

обработка на командата при изключение са разяснени подробно тук в глава 6, пункт 6.4.4

;

2.

Капани (traps). Тази

ситуация възниква на границата между две команди. Капаните

това са контролни точки, които могат да бъдат залагани умишлено от потребителя,

с цел контрол на изчислителния процес, обикновено при тестване на софтуера,

чрез вмъкване в кода на програмата на еднобайтова команда INT 3

(става дума за процесори на Intel). След обработка на прекъсването изчисленията продължават нормално от

следващата команда ;

3.

Повреди (aborts). При такива

ситуации не винаги се разполага с адреса на командата, по време на която е

настъпило изключението. По тази причина не винаги е възможен рестарт на

командата и следователно на хода на изчислителния процес. Типични изключения от

този вид са различни апаратни грешки, откривани от контролиращи логически

схеми, или при противоречиви (недопустими) стойности в системните таблици.

Заявките

за обработка на изключенията се генерират от вътрешните схеми на процесора. В

рамките на една команда могат да съществуват причини за няколко изключения, но

в даден момент ще възниква само едно изключение. Процесорът ще обработва

възникващите изключения последователно и ще рестартира машинната команда до

нейното пълно изпълнение.

Редът, в който МППОП проверява всички едновременно възникнали изключения и прекъсвания, е следният:

1.

Проверка за капан след току що

завършилата команда (постъпков режим – трасировка, или прекъсване по стойност

на резултата) ;

2.

Проверка за грешки на следващата

команда, според съдържанието в регистрите за трасиране на изпълнението. В IA-32 архитектурата те

са означени DR n (n=0¸7) ;

3.

Проверка за наличие на заявки за външни

прекъсвания ;

4.

Проверка за грешка при липса на сегмент

;

5.

Проверка за грешка при липса на

страница ;

6.

Проверка за грешка при дешифриране на

командата ;

7.

Проверка за наличие на FPU ;

8.

Проверка за грешки при операции в FPU,

ако проверката е включена.

Обслужването

на немаскируемите заявки за прекъсване по определение трябва да бъде безусловно,

но в същото време те са няколко и тяхното едновременно появяване не е

изключено. От това положение следва, че тяхното обслужване не може да бъде

друго освен последователно и за целта следва да съществува някакъв ред.

Този ред е фиксиран от конструкторите на процесора. Редът за обслужване на вътрешните и външните

немаскируеми прекъсвания за всеки процесор е фиксиран в командния цикъл чрез

съответното подреждане на условните им преходи. По-горе представеният ред се

отнася за архитектурата IA-32.

При

обслужване на заявките за прекъсване е възможна една крайно нежелателна

ситуация, наричана насищане на системата за прекъсване. Насищане

настъпва в онзи момент, когато една ЗП застига все още необслужена заявка от

същия тип. В този случай застигнатата заявка може да бъде загубена, което не е

допустимо. Насищането е параметър, който може да се свърже с максимално

допустимата честота на следване на заявките за прекъсване, която е функция от

параметъра Тр –

време за реакция (параметърът беше пояснен в предходния раздел). Влизането на

системата за прекъсване в състояние на насищане води до зацикляне, от което е

невъзможно да се излезе без допълнителна и нарочна външна намеса. Такова

състояние е възможно при некоректно поведение от страна на външното устройство,

подаващо заявка за обслужване. За борба с описаната възможна ситуация се

прилагат три подхода:

1. Решението на проблема се възлага изцяло на обслужващата програма.

След осъществяване на прекъсването, първата команда от обслужващата програма

има за задача да забрани приемането за обслужване на други ЗП до завършването

на обслужването. Обратно, преди изпълнението на командата за връщане от

прекъсване, следва да се изпълни команда, която да снеме забраната за ЗП. Този

подход следва да се прилага от процесори, които не съдържат в своята МППОП тези

защитни механизми.

2. Вторият подход се отнася до процесори, които имат един вход за ЗП и могат

сами да го контролират като управляват специален флаг за забрана и

разрешение на прекъсването. Състоянието на този флаг за текущата програма

следва да се съхранява в стека при прекъсване и след това да се възстановява.

Управлението на този флаг е възможно както от страна на МППОП, така и от страна

на програмата. В повечето случаи това е маска на прекъсванията, която може да

се поставя в една или няколко различни по отдалеченост точки по протежение на

връзката процесор – външно устройство. Възможни са и други средства за

управление в системата за прекъсване, които ще бъдат разгледани по-късно.

3. Третият подход предполага използването на динамичен вход за

сигналите за прекъсване. На входа стои асинхронен тригер работещ по фронт, така

че след фиксирането на първата ЗП, пристигането на следващи сигнали ЗП не

променят неговото състояние, докато това не направи процесора. Това гарантира,

че неконтролируемо повторение на ситуацията няма да има. За строежа и

функционирането на споменатия вид тригери читателят може да чете в книга [3].

Системата за прекъсване на всеки процесор се изгражда въз основа на определени концепции и водещи за дадените конструктори критерии. Факт е, че на пазара съществуват различни процесори и системите им за прекъсване са различни. Различията не се състоят единствено в степента им на сложност. За вътрешните прекъсвания например, различията произтичат най-вече от различията в логическата структура на процесорите, откъдето следват различни формулировки за смисъла на самите прекъсвания, различия в набора от специалните входно-изходни сигнали в системната шина на процесора, различия в набора машинни команди и не на последно място, различия в алгоритъма на МППОП. Тук ние ще се постараем да изясним основните принципи и характеристики на системите за прекъсване без да правим ретроспективни сравнения, които в големи подробности читателят може да намери в специализираните публикации.

Следва

да поясним допълнително понятието състояние на процесора. Както вече няколко пъти беше подчертавано, първото нещо, което трябва да

бъде извършено след приемане на ЗП, е да се запази текущото състояние на

процесора. С осъществяване на прекъсването процесорът по същество преминава в

друго състояние. Понятието състояние беше вече определено, но в много процесори

се въвежда още едно понятие, което дава допълнителни възможности за по-широкото

му интерпретиране. Това понятие се нарича режим на работа. Например в микропроцесорите на

фирмата Motorola са въведени два режима - системен (превилегирован) и потребителски,

а в микропроцесорите IA-32 са въведени три режима - реален, защитен и псевдо-86. Казаното

току що подкрепя тезата ни за различията. Разбира се конкретната същност на

всеки режим в реалните процесори има своята идеология, но тук е важен

принципът, който е заложен в тези възможности.

А основната идея, при реализиране на множеството режими за работа на процесора, се състои в желанието да се намали отдалечеността между отделните нива в организацията на изчислителния процес, за която говорихме в глава 2 - (концептуално ниво / програмен език) и (програмен език / командна система).

За

означаване на режима в процесора се назначава отделен регистър. Често неговите

разряди са част от регистъра на признаците. Двете отделни части информация в

този регистър характеризират от една страна текущо изпълняваното действие, а от

друга страна, в по-общ смисъл - режима, в който работи процесорът. В този план регистърът,

съдържащ тази информация се нарича регистър на състоянието.

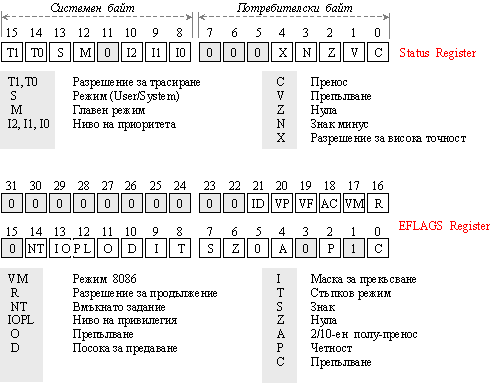

На

фигура 5.4.1.7 е представена структурата на регистъра на състоянието на две

популярни 32-битови архитектури – Motorola (MC68020), и

Intel (IA-32).

Фиг. 5.4.1.7. Регистри на състоянието

Разрядите в горните рисунки, в които има константна

стойност (0 или1) са резервирани от проектантите за използване в бъдещи модели.

Жизнеспособността на

компютърните системи се дължи на изключителната гъвкавост на системите им за

прекъсване. В по-общ план може да се каже, че това се дължи на операционната

система, която може да се определи като съвкупност от програми, които заредени

в паметта на машината, управляват нейните реакции на всяко външно или вътрешно

събитие, като при това осигуряват диалога с потребителя. Нещо повече,

операционната система е програмната среда, в която програмистът изпълнява

своите програми. Ето защо, от изключително значение е защитата на операционната

система от всякакви грешки, които могат да настъпят при изпълнение на

потребителската програма.

Именно наличието на две страни -

автоматизирана среда и потребителска програма, налага въвеждането на различните

режими за работа на процесора. Реализацията на тази идея води до значителни

архитектурни усложнения в структурата на процесорите. Изпълнението на

системните програми следва да се различава от изпълнението на потребителските

програми. Това се постига с различни подходи, но основният се състои в

разделяне на основната памет на области по предназначение. Разделянето на

адресното пространство позволява да се въведат по-ефикасни схеми за защита. Що

се отнася до работата на процесора с програми от различни области,

най-съществен е проблемът свързан със спазване

на последователността. Последователността по принцип се осигурява чрез

програмния стек, ето защо за всяка област процесорът поддържа отделен стек, а

адресирането в отделните стекове обикновено се извършва с отделни стекови

указатели. Така например, следващата таблица изразява превключването на

стековите указатели в микропроцесор МС68020, в зависимост от двата бита на

режима S и M:

Таблица 5.4.1.1

Избор на стек

|

S |

M |

Стеков

указател |

|

0 |

* |

USP - стек на потребителя |

|

1 |

0 |

ISP - стек на прекъсванията |

|

1 |

1 |

MSP - стек на супервайзора |

Запомнящите устройства тип LIFO, каквито са програмните стекове, играят огромна роля в организацията на прекъсванията в един процесор. Тук е моментът да поясним, че обемът на запомнящия масив на даден стек е пряко свързан с дълбочината на вложеност на прекъсванията, които обслужва. Така всеки стек е заплашен от препълване. Ако последното се случи, това води до срив в хода на изчислителния процес. Ето защо софтуерната организация на системата за прекъсване, както и на самите обслужващи програми, е голяма отговорност на програмиста.

От казаното става ясно, че между режимите, така както и между програмите, има необходимост от йерархия или ниво на значимост. В този именно смисъл са въведените битове №12,13 (IOPL) в EFLAGS-регистъра на процесорите IA-32 (вижте по-горе фигура 5.4.1.5). От казаното следва, че процесорът трябва да притежава определени средства за контрол и защита на своите ресурси. Механизмът на защита обикновено се състои от две части:

· Управление и защита на паметта и ;

· Защита по привилегия.

Средствата за защита на паметта откриват повечето от грешките в програмите, като например формиране на неправилни адреси, позициониране на индекса зад пределите на масива, нарушение в стека за работа с процедури и др. Защитата по привилегия открива значително по-фините грешки, както и опитите за нарушение на функционирането на системата. Терминът "привилегия" следва да се разбира като права или възможности, които обикновено не се разрешават.

При изпълнението на всяка команда се осъществява проверка на правата за защита по привилегия, т.е. постоянно се контролира текущата програма дали е достатъчно привилегирована:

·

За да употребява някои

команди ;

·

За да има достъп до

данни на други програми ;

·

За да предава

управлението на "външни за нейната среда програми".

Йерархията,

за която стана дума по-горе, най-ясно се изразява чрез командната система, в

която се различават обикновени и привилегировани машинни команди. Обикновени са онези команди, чието

изпълнение не зависи от режима, в който е установен процесорът, а привилегировани

са тези, чието изпълнение изисква смяна на режима. Така например,

привилегировани са командите, които модифицират маските за прекъсване, изменят

разпределението на паметта или влияят на механизма за защита. Може да се

обобщи, че това са командите, които работят със системните програмно достъпни

регистри.

Що се отнася до правата за достъп, следва да се отбележи, че данните на приложните програми, работещи в мултипрограмни среди, са разделени. Движението на данните между отделните нива на защита обикновено е забранено. В същото време обаче е възможно дадена програма да има достъп до данни, стоящи на нива с по-ниска привилегия.

Много програми, работещи в мултипрограмни среди, заедно с данните разделят и процедурите, например библиотеките. Правата за достъп до командния код на дадена процедура, т.е. до област, съдържаща команди, са подобни на правата за достъп до данни, но са още по-строги. Това правило обаче има изключения. Такива права са вменени на специални машинни команди, тъй като без тях приложната програма от дадено ниво не би могла да използува услугите на операционната система, най-общо казано.

Като пример за казаното отново

ще дадем архитектурата IA-32, която има 19 привилегировани

команди, групирани в три групи, според степента им на привилегированност. В

първата група са командите въздействащи на механизъма за сегментиране, които

могат да се изпълняват единствено на привилегировано ниво с номер нула, т.е. в

така наречените PL0-програми (PL - Privilege Level):

|

HLT |

- Стоп на процесора |

|

CLTS |

- Изчистване на флага за превключване на задача |

|

LGDT, LIDT, LLDT |

- Зареждане на дескрипторните таблици |

|

LMSW |

- Зареждане на думата за състоянието на процесора |

В втората група влизат още 6 команди MOV за прехвърляне на данни от или в системните регистри за управление CRn, за настройка DRn и за проверкаTRn,

Третата група включва командите, изменящи флага IF и извършващи входно/изходни операции:

|

CLI |

- Забрана за прекъсване (IF=0) |

|

STI |

- Разрешение за прекъсване (IF=1) |

|

IN, INS |

- Въвеждане от входен порт |

|

OUT, OUTS |

- Извеждане в изходен порт |

Тъй като битовете за

привилегия в IA-32 са два, то нивата, които те определят са 4. Създателите на операционната

система Windows наричат тези нива “кръгове”. Най-вътрешният кръг има ниво 0 и това е

най-привилегированата област. Програмите, които са декларирани за изпълнение в

този режим не срещат никакви ограничения. Те имат достъп до всички ресурси на

процесора и могат да извършва всички предвидени за тях манипулации. Идеята на

конструкторите е била това да бъде средата, в която би работило ядрото на една

операционна система. Средата с ниво на привилегия единица е предназначена за

функциониране на системните драйвери. Средата с ниво на привилегия две е

предназначена за някои обслужващи програми (сервиз) и в най-външната част, т.е.

в обвивката на софтуера, се разполагат потребителските приложения. И въпреки,

че хардуерът на тази архитектура предлага този избор, създателите на Windows използват само две от нивата: №0 (Ring0 или Kernel mode) и №3 (Ring3 или User mode).

Що се

отнася до прекъсванията, процесорът може да се намира в състояние "Очакване на прекъсване", или

в състояние "Работа".

Установяване на начина за интерпретация на заявките за прекъсване се постига

със специални машинни команди, но по същество тази възможност е заложена в

командния цикъл и алгоритмите на локалните контролери. Ситуациите са

многобройни, а алгоритмите са изключително сложни, което се определя от

сложната логическа структура на процесора и на неговите устройства, подчинена

на организационни принцип за паралелно и асинхронно функциониране, нещо за

което вече говорихме в тази глава. Различни аспекти на тези проблеми ще бъдат

изяснени допълнително тук в глава 6.

Смяната на режима се постига със специална привилегирована команда за системно извикване. Тези команди предизвикват така нареченото програмно прекъсване, с изменение на режима. Важното е да се знае, че при това специално прекъсване, състоянието на процесора се съхранява в стека на онзи режим, в който се преминава.

Следващият раздел е:

5.4.2. Обозначаване на

прекъсванията