Последната актуализация на този раздел е от 2020 година.

5.5.2 Шини.

Синхронен и асинхронен обмен. Арбитриране на шинния обмен – Продължение 3

Множеството крупни функционални елементи в структурата на всяка компютърна система се нуждае от обмен на информация за да функционира. За този именно обмен е необходима подходяща система от връзки (съединения). Системата от връзки трябва да осигурява обмен на информация между:

·

Процесорните елементи и паметта ;

·

Процесорните елементи и елементите на

входно-изходната система ;

·

Системата на паметта и елементите на

входно-изходната система.

С развитието на компютърните системи се развиват и системите за връзка с отделните елементи в структурата и с външния свят. Повечето компютърни системи съдържат няколко различни шини, всяка от които е оптимизирана към определен вид комуникация. Част от шините е скрита във вътрешността на интегралните схеми или е достъпна само в рамките на печатната платка. Има шини, които са достъпни отвън с цел подключване на допълнителни устройства. Обикновено тези шини са стандартизирани, което позволява подключване на еднотипни устройства произведени от различни производители. За да характеризира дадена шина, е необходимо да се знае:

· Съвкупността на сигналните линии ;

· Физическите, механическите и електрическите характеристики на шината ;

· Съвкупността от сигнали за синхронизация, за управление, за състояние, за арбитриране ;

· Правилата за взаимодействие на присъединените към шината устройства (протокол на шината).

Операциите върху шината се наричат транзакции. Основните видове транзакции са транзакция за четене и транзакция за запис, или още транзакция за въвеждане или за извеждане (когато става дума за външни устройства). Шинната транзакция включва две противоположни по посока съставящи – изпращане на адрес и приемане на данни.

Когато две устройства обменят информация посредством дадена шина, едно от тях инициира и управлява обмена. Такова устройство се нарича водещо (bus master). Водещо е всяко устройство, което може да заяви и в последствие да владее управлението на шината, т.е. да управлява трансфера на данни. Водещият не е задължен да използва данните сам. Той може да прави това в интерес на друго устройство. Устройствата, които не могат да инициират транзакции, се именуват водени (bus slave). Тъй като към шината могат да бъдат присъединени няколко водещи устройства, тя има магистрална организация, нещо което ще поясним малко по-късно. За получаване на правото да се владее, т.е. да се управлява шината, водещите устройства се подлагат на арбитриране.

Целевото предназначение на дадена шина определя нейните параметри. Така се класифицират три типа шини:

· Шини “процесор-памет" ;

· Шини за вход-изход ;

· Системни (управляващи) шини.

В съвременните

микропроцесори ефективността налага обменът между процесора и оперативната

памет да се осъществява по независима шина. Тази шина се нарича предна шина FSB (Front-Side Bus). В групата на шините

"процесор-памет” се включва и шината за връзка с кеш паметта. Тук става

дума за задна или вторична шина BSB (Back-Side Bus). Независимият обмен на

процесора с оперативната памет и с кеш паметта обединява FSB и BSB в архитектура,

известна като DIB (Dual Independent Bus).

Шините за вход-изход свързват процесора (паметта) с входно-изходните устройства. Отчитайки разнообразието на тези устройства, шините за вход-изход се унифицират и стандартизират. Поради по-ниските скорости за обмен с болшинството външни устройства от шините за В/И не се изисква висока пропускателна способност. При конструиране на тези шини се преследва ниска цена и в същото време възможно по-голяма дължина на линиите.

С цел на се намали общата цена на компютърната система много от тях се проектират с обща шина за памет и за Б/И устройства. Такива шини често се наричат системни. Системната шина служи (често наричана backplane bus) за физическо и логическо обединяване на всички устройства.

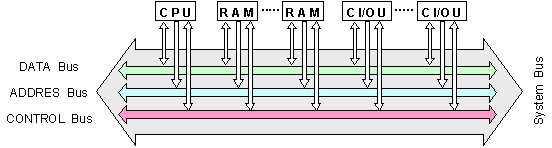

Фиг. 5.5.2.16. Структура на системната шина

Всяка транзакция по системната шина започва от ведущото устройство с поставяне на адресната информация. Адресът позволява да се избере воденото устройство и да се установи връзка между тях. За целта се използва онази част от системните линии, които се наричат адресна шина. По АШ може да се подава адрес на клетка от паметта, номер на регистър от регистровия файл на процесора, адрес на порт за В/И и пр. Многообразието на адресната информация предполага допълнителна информация за уточняване вида на адреса. Такава информация се съдържа косвено в самия адрес, но е възможно да се предава по линии със специално предназначение, които са част от шината за управление УШ. В някои шини е предвиден адрес, с който се оповестява цяла група водени устройства (broadcast). Ширината на адресната шина обикновено е 36[b], но може да достига до 40[b].

Данновата шина има ширина, която е кратна на байт и може да достига от 32[b] до 128[b]. Този параметър еволюира заедно с цялата платформа, така че читателят следва да го приема тук само като информативен. Освен това ширината на данновата шина в байтове следва да бъде кратна на степените на числото 2. Ширината на ДШ съществено влияе на производителността на компютърната система. В повечето системи адресът е адрес на една адресируема единица, а това е клетка с дължина 8 [b]. В случай на транзакция на данни с по-къси формати се използват младшите линии в ДШ. Съществуват компютърни системи, в които за транзакции на адрес и на данни се използват едни и същи линии. Такива системи имат мултиплексируеми по предназначение шини. Нещо повече, в такива шини се налага пренасочване на линиите – в даден момент те са изходни спрямо процесора, а в други моменти са входни. Основната причина, по която се практикува тази организация е необходимостта от минимизиране на изводите на интегралната схема.

Съвкупността от линии, предназначени за разпространение на управляващи сигнали, е определена като управляваща шина УШ. Линиите в състава на УШ могат да се разделят на следните групи:

1.

Сигнали за управление на транзакциите,

които определят:

·

Тип на транзакцията (четене или запис) ;

·

Брой на байтовете, предавани по ДШ (ако

се предава част от цялата дума, номерата на байтовете) ;

·

Типа на адреса подаден по АШ ;

·

Вида на протокола, който следва да се

приложи.

За постигане на изброените цели обикновено се отделят от 2 до 8 сигнални линии.

2. Към втората група сигнални линии се причисляват тези, които са предназначени да пренасят информация за състоянието (status) на воденото устройство. Тук обикновено се отделят до 4 сигнални линии. Може да се интерпретират отделни битове или като код на грешка ;

3. В третата група са включени линиите за арбитраж. Арбитрирането е свързано с обработка на заявките от страна на водещите устройства, претендиращи за заемане на шината и осъществяване на транзакция. Броят на арбитражните линии в различните шини варира от 3 до 11 ;

4. В четвъртата група са включени сигналните линии на заявките за прекъсване. Заявките за прекъсване се издават от водените устройства, когато те искат да бъдат обслужени. При няколко заявки в контролера на прекъсванията се извършва избор, за което вече писахме в предходни раздели ;

5. Сигнални линии, предназначени за организация на локални мрежи. Общо приетата практика налага от 1 до 4 такива линии. Това се мотивира с това, че последователното предаване на данни протича значително бавно в сравнение с паралелното, и мрежите е изгодно да се реализират без бързи линии за адрес и данни. В определени ситуации тези линии могат да имат и други функции ;

6. В някои УШ е възможна и 6-та група сигнални линии - от 4 до 5 линии за позиционен код. Те се подключват към отделни изводи на куплунга. С помощта на мостчета на тези изводи може да бъде зададен уникален позиционен код за дънната платка или за дъщерна платка.

И последно, във всяка шина присъстват линии за тактуване и синхронизация. В зависимост от протокола за транзакции (синхронен или асинхронен) линиите могат да бъдат от 2 до 6.

Не бива да забравяме и линиите за захранване и за зануляване.

Връзки и конфликти на връзките.

Арбитър

Видовете връзки от гледна точка на организацията бяха определени в глава 2. Връзките за трансфер на данни, който обсъждаме тук, са с магистрална организация. Същността на магистралната организация се състои в принципа “един предава – всички могат да приемат”. С други думи, магистралната връзка е общ ресурс и в този смисъл поражда проблем за своите ползуватели в случай, че няколко от тях едновременно изявят желание да се възползват от нея. Проблемът се състои в това, че въпреки едновременно заявената необходимост за използване на магистралата, която по-често се нарича шина, това не е възможно поради опроводяването по принципа “обща точка”, който не позволява върху шината да бъдат поставени за трансфер данните на повече от един предавател, които съответният приемник ще приема. Така от тази гледна точка, логическите устройства, които са включени към шината, се класифицират както следва:

· Арбитър на шината – устройство, което осъществява контрол над заетостта на шината ;

· Водещо устройство (или още Master – господар, главно устройство) – това е онова устройство, което е подало заявка за заемане на шината и е получило от арбитъра правото да се разпорежда с нея, т.е. устройството проявило инициативата за обмен ;

· Водимо устройство (или още Slave – слуга, подчинено устройство) – това е онова устройство, което ще изпълни трансферната операция по команда, подадена от водещото устройство.

От гледна точка на входно-изходната операция, изложената класификация се отнася за всички устройства, подключени към шината, включително и за процесора. Всяко едно от тях може да поиска да владее шината и ако получи това право се определя като Bus Master. Съответно, устройството, което ще бъде присъединено за изпълнение на операцията, се определя като Slave. Най-често прилаганият принцип при арбитриране на заявките, т.е. при осъществяване на избора, е принципът “Първият срещнат според приоритетния ред ”. Приоритетът в някои арбитражни схеми може да се променя според назначения от програмата режим. Промяната е аналогична на описаната такава за контролера на прекъсванията. Принципът на първия срещнат (или още на случайния избор) вече описахме и неговата апаратна реализация е известна на читателя, например, като схема за избор в асоциативното запомнящо устройство (вижте фигура 4.4.3), или още като схема за апаратен полинг на заявки за прекъсване (вижте фигура 5.4.3.3), или като схема за избор с разпределени функции (вижте фигура 5.4.4.3 и 5.4.4.4). Концептуално проблемът избор е изявен и разгледан още в глава 6, тъй като е свързан с управлението на буферните памети. Там са представени и други разбирания, върху които се реализира избор, както и съответните им схемни решения.

Реализацията на арбитражните функции зависи от концепциите за организация на интерфейса по дадена шина. Ако се съсредоточим обаче върху самия арбитраж, може да кажем, че той има два варианта на реализация - централизиран и децентрализиран.

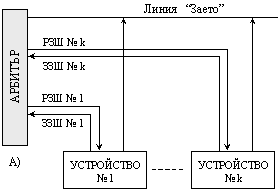

Централизиран арбитраж

Възможни са три схеми за организация на този арбитраж. Първата от тях се характеризира с това, че всяко устройство притежава своя отделна двойка линии в шината, която го свързва с арбитъра. Чрез изходната линия устройството подава сигнал заявка за заемане на шината (ЗЗШ), а по входната получава отговор от арбитъра за това има ли право да управлява шината – сигнал разрешение за заемане на шината (РЗШ). Казаното е илюстрирано чрез рисунка А) от фигура 5.5.2.17.

Фиг. 5.5.2.17. Схеми за централизиран арбитраж

Логическата схема за избор на заявка за заемане на шината, която е същността на арбитъра, е реализирана чрез еднотактна схема за избор, въз основа на приписания на входовете приоритет. Полинг сигналът в тази схема се генерира в отговор на постъпилата заявка, ако шината не е заета. Избраната по този начин заявка връща към съответното устройство сигнал за разрешение РЗШ. С получаването на този сигнал устройството обявява на всички останали, че е заело шината като поставя своя флаг “Заето” върху едноименната линия от шината. Тя е обща за всички устройства и на практика реализира сигнала “Заето” към арбитъра, чрез опроводено ИЛИ. При получаване на сигнала “Заето” арбитърът се установява в изходно състояние. Следващ сеанс за избор арбитърът може да осъществи след като шината се освободи.

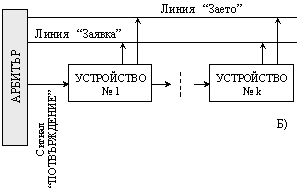

Втората схема за организация е илюстрирана с рисунка Б) от същата фигура. Тук арбитърът има само едни вход за всички ЗЗШ. Сигналът към арбитъра се реализира също чрез опроводено ИЛИ. Ако шината не е заета, арбитърът стартира избора на устройство, като подава сигнал “Потвърждение”. Този сигнал се разпространява последователно през контролерите на устройствата. Разпространението се допуска от текущото устройство, ако то не е подало ЗЗШ и се забранява, ако е подало такава. В последния случай избраното устройство блокира по-нататъшното разпространение на сигнала “Потвърждение” и оповестява правото си да управлява шината чрез флаг “Заето” върху линията на сигнала “Заето”. След този сигнал поведението на арбитъра е аналогично на описаното за първи вариант.

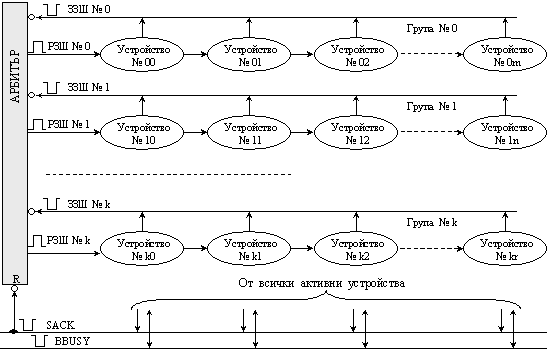

Често описаните две схеми за свързване на външните устройства се комбинира. Получава се така, че към арбитъра не се подключват k на брой отделни устройства, както е показва вариант А), а k на брой групи от еднотипни устройства, които в рамката на всяка отделна група се арбитрират последователно, както илюстрира вариант Б). Така се получава следната матрично организирана съвкупност от устройства:

Фиг. 5.5.2.18. Комбинирана схема за централизиран арбитраж

В тази схема най-приоритетна е групата с номер нула. Във всяка група най-приоритетно е най-лявото устройство. Активните устройства по своя инициатива и независимо едно от друго генерират заявки за заемане на шината ЗЗШ. Заявките се обединяват върху съответните линии чрез монтажно ИЛИ. Арбитърът извършва избор върху подадените ЗЗШ и издава само едно разрешение върху съответната линия РЗШ. Изборът измежду конкуриращите се заявки се извършва според най-малкия им номер. Ако съществува конкуренция между устройства в рамките на избраната група, правото да владее шината се пада на най-лявото от активните устройства.

Линията SACK оповестява арбитъра, че издаденият от него разрешаващ сигнал е достигнал избраното устройство. От своя страна, при получаване на този отговор, арбитърът прекратява подаването на сигнала РЗШ по съответната линия. Линията BBUSY е предназначена за оповестяване на всички активни устройства (и по-точно на очакващото), че магистралата все още не е освободена. Когато магистралата се освободи, очакващото правото си устройство само установява този сигнал като при това снема и изпращания към арбитъра сигнал SACK, с което арбитърът се подготвя за следващ избор. На следващата фигура е представен процесът на заемане на шината.

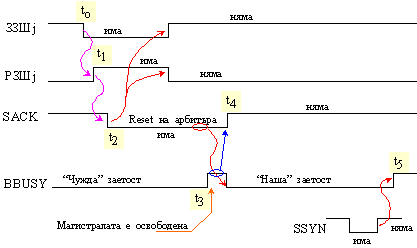

Фиг. 5.5.2.19. Времедиаграма при заемане на шината

В момент t0 “нашето” активно устройство формира на линията ЗЗШ в своята група логическа нула, който достига арбитъра. В отговор в момент t1 “нашето” устройство получава сигнал разрешение РЗШ като логическа единица. Сигналите РЗШ се подават във вид на единица за разлика от всички останали логически сигнали в системната шина. Нашето активно устройство “поглъща” разрешението като не му позволява разпространение към следващите устройства в групата. За успешното приемане на сигнала разрешение нашето устройство оповестява арбитъра в момент t2 като поставя логическа нула на линията SACK и остава в очакване на освобождаването на магистралата от “чуждата” заетост. “Виждайки”, че магистралата се е освободила (момент t3), нашето устройство само формира сигнал заета, подавайки на линия BBUSY логическа нула в момент t4. От този момент нататък арбитърът започва нов цикъл за приемане на заявки ЗЗШ. През това време “нашето” устройство осъществява обмен на данни. След получаване от подчиненото устройство на потвърждението за успешен обмен SSYN под формата на логическа нула, “нашето” устройство освобождава магистралата (момент t5), прекратявайки сигнала BBUSY.

В зависимост от вида на обмена за водещото устройство върху магистралата се дефинират цикли на операция Запис, на операция Четене, на операция “Четене-Модификация-Запис”, а така също цикъл “Прекъсване. В зависимост от вида на магистралата, или най-общо казано, от вида на интерфейса, времедиаграмите на тези цикли са различни. Това което следва ясно да се разбере тук е това, че арбитрирането е свързано със своеобразен диалог между участниците в системата.

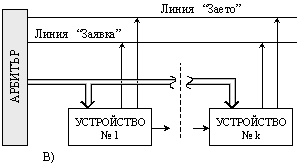

Третата схема за организация на арбитража е илюстрирана с рисунка В) от фигура 5.5.2.17 по-горе. Тук към арбитъра са подключени две линии опроводено ИЛИ – на заявките и на сигнала “Заето”. Устройствата и арбитърът са свързани още с допълнителна шина, с помощта на която се извършва проверка на приоритета и на готовността на устройствата.

Децентрализиран арбитраж

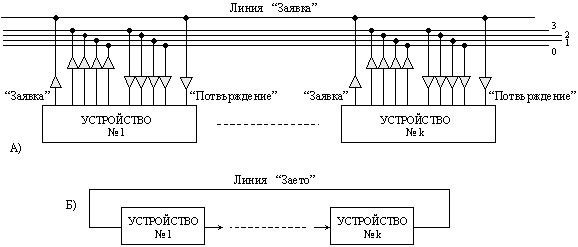

В този вариант на организация не се наблюдава наличието на отделно реализирана схема за избор. Апаратното оборудване за арбитриране на шината се съдържа в интерфейса на всяко устройство, което се подключва към шината. Ще представим две схеми за организация на избора. В първата схема всички устройства са свързани линейно чрез сигналите “Заявка” и “Потвърждение”, както е показано с рисунка А) на фигура 5.5.2.20.

Фиг. 5.5.2.20. Схеми за децентрализиран арбитраж

Както се вижда, сигналите “Заявка”, които излизат от всяко устройство са общо опроводени в схема ИЛИ, т.е. формират логическа дезюнкция. Това се постига чрез схеми, чиито изходи са с отворен колектор (дрейн). Същата линия се подава отново на всяко устройство, но в качеството й на сигнал “Потвърждение”. За да добие смисъл това опроводяване, чрез аналогично свързване всички устройства разпространяват своя код. На рисунката, за всяко устройство е показан 4-битов изход заедно с 4-битов вход. Логиката на опроводяването е следната: ако дадено устройство подаде заявка за заемане на шината заедно със своя код и в отговор получи сигнал потвърждение заедно със непроменения си код, това означава, че е завладяло шината и може да започне трансфера на данни. В случай, че върху общо опроводената кодова шина поставят своя номер няколко устройства едновременно, то се твърди, че резултантният код, който обратно ще получат всички устройства, е най-големия номер измежду подадените. Само едно от тези устройства ще разпознае във върнатия код своя номер и това устройство ще владее шината. В този смисъл може да се каже, че най-приоритетно е устройството с №k.

Ще докажем, че изказаното твърдение е вярно: Нека две устройства, съответно №5 и №6 подадат едновременно заявка за заемане на шината. Това означава поразрядна дезюнкция от следните два кода: (0101)È(0110). Резултатът е комбинацията 7=0111. Тази комбинация получават обратно всички устройства. Получената комбинация всяко устройство подлага на вътрешно сравнение със своя идентификационен номер, като прилага следните действия:

Сравнението започва от старшите битове в посока към младшите. Ако устройството установи пълно съвпадение, това значи че е спечелило шината. Ако обаче установи различие в даден текущ бит, изходният буфер на този бит, заедно с всички следващи по-младши изходни буфери, се изключват (минават в състояние на висок импеданс). В резултат на тези действия включени в пълен състав ще останат само буферите на спечелилото шината устройство.

Приложението на тази логика върху дадения по-горе пример означава следното – устройство №5 получавайки код 0111, установява различие в бит b1 между изходната (0) и получената (1) стойности. В резултат на това изключва двата младши изходни буфера (в бит №1 и №0). В резултат на това действие на устройство №5 стойността на резултантния код върху общо опроводената кодова шина се променя и става 0110=6. В същото време същото действие изпълнява и устройство №6, което установявайки различие в бит №0, също изключва младшия си изходен буфер, с което препотвърждава кодовата комбинация 0110 върху кодовата шина. Тъй като продължава да постъпва в устройство №6 през неговите входни буфери, в крайна сметка то се разпознава като устройството завладяло данновата магистрала.

Втората схема е крайно опростена, но и по-бавна. Всички устройства се обхванати с кръговата линия “Заето”, както се вижда на рисунка Б) от горната фигура. По тази линия циркулира от устройство към устройство маркерен импулс (или серия импулси) и по начина на преминаване по кръга се определя заетостта на информационния канал. Когато дадено устройство поиска да управлява шината, то задържа този маркер (когато той го достигне) и не го пропуска към следващото устройство.

Децентрализираният арбитраж се приема за по-надежден, тъй като функционирането на шината не зависи от едно единствено устройство. Описаната като първа по-горе схема за арбитриране се прилага например в шини по стандарта SCSI.

Понятие за синхронен и асинхронен

обмен. Синхронни и асинхронни шини

Понятие

за цикъл на обмен

Входно-изходният обмен в съвременните системи протича в така наречените цикли на обмен. Под цикъл на обмен се разбира времеви интервал, в течение на който протича една операция на обмен. В рамките на един цикъл най-често се предават няколко порции данни, поради което се говори за блочен или пакетен режим на обмен. Тук под порция данни разбираме двоична комбинация с определена дължина (8, 16, 32, 64-битова, или друга), чиито битове съществуват върху отделни паралелни линии едновременно във времето. Обикновено такава връзка се определя като паралелна, а обменът по нея се нарича паралелен. При блочния и при пакетния обмен обаче се има предвид непрекъснато но последователно предаване на порции данни върху паралелна шина. В зависимост от броя на информационните линии в шината организацията на обмен може да бъде изяло последователна. Ако връзката е еднопроводна, обменът е последователен бит след бит. В такива случаи се говори, че се обменят кадри или фреймове. Тези информационни последователности имат специална структура, част от която са самите данни.

От гледна точка на водещото операцията устройство (Master-устройството), циклите се определят като:

· Цикъл за запис, или още за извеждане ;

· Цикъл за четене, или още за въвеждане.

Съществуват още цикли от типа “четене-модификация-запис” или “въвеждане-пауза-извеждане”. Наличието или отсъствието на даден тип цикъл се определя от особеностите на процесора, от особеностите на шината и от особеностите на външното устройство.

Всеки тип цикъл определя строг състав от управляващи сигнали и строга последователност за същите, която е прието да се нарича протокол на обмена. Продължителността на цикъла може да бъде постоянна или променлива. В системи с една шина циклите от тип четене и от тип запис се редуват върху шината. В системи с повече от една шина различните по тип цикли могат да се изпълняват едновременно.

Явлението skew (изкривяване)

Паралелните шини

се образуват от паралелни връзки. Полагането на паралелните връзки на практика

върху печатните платки е затруднено по редица причини: елементите се намират на

различни разстояния; различните линии имат различен брой разклонения;

различните линии имат различна топология; имат и различно натоварване; минават

в различни нива на многослойните платки; имат различен брой преходи от едно

ниво към друго; имат по същество различна стойност на монтажния капацитет. Тези

и други фактори на реалната експлоатация оказват решаващо влияние при

преследването на пределните тактови честоти за дадено промишлено произведение.

В тези условия е изявено явлението изкривяване на разпространяващите по

отделните линии на шината сигнали.

Същността

на това явление се състои в това, че едновременно издаваните битове данни

достигат местоназначението си не едновременно. Ситуацията изключително

много прилича на коронната дисциплина в леката атлетика – 100 метровия спринт

на група състезатели. Всички тръгват едновременно, но пристигат на финала с различни

закъснения! В нашата интерпретация, приемането на правилни стойности за

данните, е от най-съществено значение, което означава, че за тази цел периодът

на тактовия сигнал трябва да бъде гарантирано по-голям от максималното

разсейване, с което данните могат да се появят и в най-отдалечената точка.

Явлението skew ограничава желанието за разширяване на шините. Още през

90-те години на миналия век започва усвояването на тактови честоти над 100[MHz]

за синхронизиране на шините. При честоти от този порядък периодът на сигнала

пада под 1[ns]. За времето от една наносекунда фронтът на даден сигнал, който

се разпространява със скоростта на светлината, може да измине не повече от 25

сантиметра разстояние. Ето защо да се достигне съизмеримо разсейване на 32 или

64 битови паралелно стартирали сигнала в рамките на времеви квант от този

порядък, вече става възможно само за много компактни конструкции на печатните

платки. Разпространението на данни по гъвкави кабели и на разстояния от

порядъка на 10 сантиметра остава в рамките на синхронизация в пределите на

няколко десетки кило херца.

За да се

повиши пропускателната способност на шината (без да се повишава

синхронизиращата честота) се прилага така нареченото двойно синхронизиране

(DDR, Dual Data Rate), което ние пояснихме в глава 4 (вижте фигура 4.2.2.6). Вместо само по единият фронт данни върху шината се издават и по двата

фронта на тактовия импулс. За да имат еднакъв шанс двете порции в рамките на

едни период на сигнала, последният се реализира с коефициент на запълване 50%.

Тези модификации се съдържат в режимите UltraDMA на интерфейса ATA, на

интерфейса SCSI и неговите разновидности, а така също в паметите от тип DDR и

SDRAM.

При

високи честоти се прилага още принципът на собствена синхронизация (source

synchronous transfer). В този случай източниците на данни сами излъчват

синхронизиращия сигнал, а той за различните устройства може да е различен. Така

се постига по-добро съвместяване между данните и синхроимпулсите, тъй като те

се разпространяват в една и съща посока.

Повишаването

на работните честоти се съпровожда с понижаване на логическите нива на

сигналите – от 5 на 3,3 и до 1,5 волта и дори до 0,8 волта за AGP-шините.

Понятие и определения за шина

Вече многократно ни се наложи да употребяваме понятието шина. Тук това понятие употребяваме в смисъла на разглежданата тематика. В този контекст това не е просто логическа връзка между два структурни елемента, а връзка за реализация на трансфер с магистрална организация. Понятието шина е събирателно, твърде обобщено. В нейния състав влизат отделни шини (групи съединителни линии), разпространяващи специфична информация, в смисъла на която формират:

1. Информационен канал ;

2. Магистрала за управление на информационния канал.

По информационния канал се предават:

1. Кодове на данни ;

2. Кодове на адреси ;

3. Кодове на команди ;

4. Кодове на състоянията.

Информационният канал съдържа адресна шина и даннова шина, а магистралата за управление на информационния канал съдържа:

· Шина за предаване на управлението (линии свързани с арбитража) ;

· Шина за управление на обмена (синхронизация) ;

· Шина за прекъсванията ;

· Шина на специални сигнали (контрол на захранването, общ сигнал Reset, контролни кодове за откриване и поправка на грешки при предаване и други задължителни и незадължителни линии).

Данновата шина обикновено се разбира като паралелна (има определена ширина, която се измерва в битове). Тя е основна шина и е двупосочна, тъй като реализира обмен във двете посоки. Подключването на устройствата към данновата шина се осъществява чрез буфери с три състояния. Последното се налага поради нейната двупосочна и магистрална организация. Ширината на данновата шина е най-съществената характеристика и определя (именова) дадена шина като например, 32-битова. Освен това определя редица други технически характеристики като например, максималната скорост за трансфер на данни.

Втора по значение е адресната шина. Нейната ширина е свързана с дължината на адреса, който използва даденият процесор. От гледна точка на процесора тази шина е еднопосочна. Възможно е тази шина да се използва и за трансфер на друга информация, например, данни. В такива случаи тя се определя като мултиплексна, т.е. като шина, която превключва своето предназначение. Основната причина да се прави това, е стремеж към минимизиране на физическите връзки, а оттам поевтиняване на системата като цяло (вижте в началото фигура 5.5.2.1).

Управляващата шина е помощна. Нейният състав при различните интерфейсни шини е твърде различен. Общо е обаче разбирането, че в нейния състав са включени онези линии, които разпространяват управляващите сигнали, като код на операцията, сигнали за разрешение, за валидност, признаци за състояние и за грешки и други специфични за концепцията на шината стойности. Отделните линии в управляващата шина могат да бъдат едно или двупосочни. За тези линии от особено значение е новото на активната логическа стойност. Говорим, че управлението е по нулата или по единицата. Основното предназначение на управляващата шина е да осъществи и контролира синхронизацията между обменящите се устройства. Особено значение за надеждността на процеса на обмен имат фронтовете на управляващите сигнали. Моментите, в които се появяват тези фронтове маркират и реализират във времето съответния шинен протокол, или казано с други думи, реализират в крайна сметка фиксирането на данните по предназначение. Сигналите, които непосредствено извършват това, се наричат строб-сигнали. Строб сигналите могат да се определят още като строб за четене и строб за запис.

В зависимост от протокола, т.е. от алгоритъма, по който се реализира обменът по шината, последният се определя цялостно като:

· Синхронен. Обменът, а от там и шината, се определят като синхронни, когато инициаторът на обмена (процесор, контролер) приключва обмена в рамките на установен от него времеви интервал, т.е.без да се интересува от интересите на изпълнителното (подчиненото или воденото) устройство ;

· Асинхронен. Този обмен и такава шина се определят като асинхронни, когато инициаторът на обмена е в диалогова връзка с подчиненото устройство. Инициаторът приключва (завършва) обмена след като получи от изпълнителя специален сигнал потвърждение.

Синхронен обмен

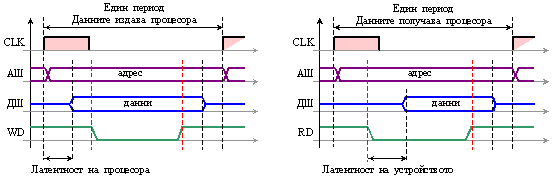

Ще се спрем най-напред на синхронния обмен. Синхронизацията се постига чрез специален периодичен правоъгълен сигнал с определена честота, определяща темпа на работа на всички устройства, които го използват. В общият случай в трансфера вземат участие следните елементи – адрес, данни, строб на кода на операцията и сигнали на допълнителните условия. В зависимост от това кой е източникът на данните и какво е неговото закъснение при генериране на данните са възможни следните времедиаграми:

Фиг. 5.5.2.21. Еднотактов синхронен обмен

Данните, излизащи от процесора се съпровождат от строб-сигнала за запис WD. За надеждност на записа процесорът продължава да поддържа данните в рамките на текущия цикъл и след изчезване на записващият строб. При обратния обмен данните подава външно устройство (контролер), което обикновено има по-голяма латентност. В отговор на строб-сигнала за четене RD, който процесорът издава, устройството поставя данните върху шината, а в отговор на изчезването на строб-сигнала – ги снема от шината. И в двата случая данните изчезват от шината след стробиращите сигнали.

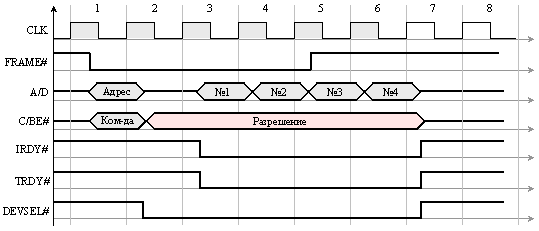

Освен еднотактен цикълът на синхронен обмен може да бъде многотактен. Многотактните цикли могат да бъдат с фиксирана и неограничена продължителност. Ще дадем още един пример за синхронен обмен въз основа на най-разпространената към момента системна шина по стандарта PCI. Цикълът на обмен по тази шина не е фиксиран по продължителност и се нарича транзакция. Един период на синхросигнала в транзакцията се нарича фаза. Ще ни бъдат необходими още следните означения:

· CLK – Синхронизираща последователност на шината (от 33 до 66[MHz]) ;

· FRAME# - Сигнал активна нула, издаван от устройството инициатор на трансфера, определящ продължителността на транзакцията ;

· A/D – 32 или 64 битова шина за предаване на адрес и данни. Шината е мултиплексна ;

· C/BE# - Представлява шина от 4 линии за команда (С) и за масив байтове (ByteEnable#) ;

· IRDY#, TRDY# - Сигнали, показващи готовността на устройството инициатор и на целевото устройство ;

· DEVSEL# - Сигнал отговор на целевото устройство за това, че разпознало своя адрес и е готово за трансферната операция ;

· IDSEL# - Сигнал за избор на устройство след конфигуриране от тип CS (Chip Select) .

Основно положение в PCI-шината е, че адресът се предава в началото на транзакцията и се съхранява в буферен регистър в целевото устройство. Така в последствие линиите на шината A/D се използват за трансфера на данните. На следващата фигура е изобразен трансфер на 4 последователни порции данни. Всички превключвания по шината са синхронизирани по предния фронт на сигнала CLK. Допустимите конкретни стойности на закъсненията, както и останалите сигнали, които са дефинирани за PCI-шината, читателят може да узнае от пълното описание на стандарта и неговите модификации. За нас тук сега те са принципно без значение.

Фиг. 5.5.2.22. Синхронен обмен по PCI-шина

Представената транзакция на 4 последователни порции данни (примерно 4х4 байта) отнема 6 периода (6 такта или още 6 фази). В първата фаза инициаторът на трансфера генерира сигнала FRAME# и заедно с него поставя на шината 32-битов адрес и 4-битова команда. Командата е за операция четене и се отнася за оперативната памет. Оперативната памет при тези сигнали следва да съхрани изпратения адрес за да го използва за организиране на последователния достъп, а той ще продължи, докато не изчезна разрешението, което се явява по шината C/BE# веднага след командата във втора фаза. Инициаторът използва втория такт за да превключи шината A/D като входна, тъй като по нея ще приеме изпратените данни. Докато инициаторът изключва за да пренасочи входно-изходните буфери на шината A/D, целевото устройство включва своите изходни буфери и установява сигнала DEVSEL#, с което оповестява, че е получило командата за трансфер.

По време на трансфера инициаторът поддържа активни определен брой линии от шината C/BE#. Логиката на това поддържане се съдържа във възможностите на целевото устройство. Ако то има 32 битова изходна шина, тогава инициаторът поддържа активни и четирите линии BE#, в противен случай само възможния брой.

В началото на третия такт инициаторът активира сигнала IRDY#, с което съобщава за собствената си готовност да приема данни. В същото време целевото устройство активира своето потвърждение чрез сигнала TRDY#, като заедно с това поставя порция данни №1 върху шината. В края на такта инициаторът фиксира получените данни в своя буфер. Така в началото на всяка следваща фаза целевото устройство издава поредната порция данни, а инициаторът я приема в края на фазата. За оповестяване края на трансфера инициаторът използва сигнала FRAME#, чиято активна нула снема в предпоследния такт, който в дадения пример е 5-ти. В края на 6-ти такт инициаторът фиксира последната порция, след което по време на 7-ми такт както той, така и целевото устройство. възстановяват изходното си състояние и освобождават шината.

Двустранните сигнали за готовност IRDY# и TRDY# могат да бъдат прекратявани по време на трансфера, ако някой от участниците загуби готовността си. Това може да бъде причина за удължаване на съответната фаза, без обаче да се счита, че трансферът е прекратен. Успешна е всяка фаза, по време на която и двата сигнала са активни.

Главното достойнство на синхронния обмен се състои в простотата на протокола и минималния брой управляващи сигнали. Недостатъците се изразяват главно в липсата на диалог, т.е. в това, че отсъстват гаранции за това, че изпълнителят ще изпълни зададената операция. Освен това синхронизацията налага високи изисквания към бързодействието на изпълнителя.

Асинхронен обмен

Асинхронният метод за организация се постига с помощта на две групи сигнали - управляващи и оповестяващи. Тези две групи сигнали свързват инициатора и изпълнителя и са част от шината за обмен. Процесът на обмен е своеобразен диалог, който се провежда между свързалите се по шината устройства и също се нарича протокол.

Основното достойнство на асинхронния обмен се изразява в по-високата надеждност при предаване на данните. Протоколът за обмен е изключително гъвкав и адаптируем, така че е в състояние да организира и осъществи обмен между устройства със силно различаващи се скоростни показатели. Недостатъкът се изразява главно в големия брой сигнали. Колкото по-прецизен е алгоритъмът на диалога и колкото повече различни ситуации са вградени в него, толкова повече са сигналите на шината.

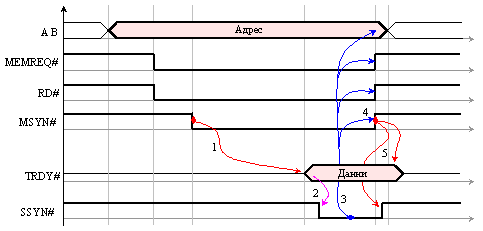

Ще поясним асинхронния обмен на примерна времедиаграма върху шина, в чийто състав влизат:

· АВ – Адресна шина. По нея се предава адрес и команда към подчиненото устройство ;

· DB – Даннова шина ;

· MEMREQ# – (Memory Request) заявка за обмен с паметта ;

· RD# – (Read) код на операцията четене, която ще изпълни подчиненото устройство ;

· MSYN# – (Master Synchronization) сигнал за начало на обмена ;

· SSYN# – (Slave Synchronization) сигнал отговор от подчиненото устройство.

Фиг. 5.5.2.23. Асинхронен обмен (операция четене)

Инициаторът на обмена издава адрес и го поддържа по време на трансфера, след което изпраща с необходимите закъснения заявката до нужното изпълнително устройство заедно с кода на операцията. Тези, както и други възможни действия от страна на инициатора, подготвят обмена и след като подготовката завърши, издава сигнала MSYN# .

В отговор на този сигнал подчиненото устройство започва да изпълнява операцията. Разбира се, това то прави с присъщата си скорост. Когато данните са извлечени и заредени в изходния буфер, заедно с тях устройството издава синхронизиращия сигнал SSYN#. Инициаторът, който до момента е бил в очакване, получавайки този сигнал, разбира, че данните са върху шината и ги фиксира в своя буфер. Данните в представената времедиаграма следва да се разбират обобщено – това може да е една порция, но може да бъде и блок. Трансферът на блок обаче изисква допълнителни синхронизиращи сигнали, които не са показани. Трансферът по принцип се прекратява от инициатора чрез снемане на сигнала MSYN# .

Когато водещото устройство фиксира успешно в своя буфер получените данни, то снема от шината сигнала MSYN#. Заедно с този сигнал инициаторът прекратява (в съответния ред) подаването и на останалата информация – адрес, команда, избор на устройство. В същото време, за подчиненото устройство изчезването на този сигнал означава, че данните са достигнали успешно предназначението си и трансферът ще бъде закрит. Така в отговор подчиненото устройство снема от шината активната стойност на сигнала SSYN# и изключва своите изходни буфери.

Асинхронният обмен се основава на причинно-следствените връзки и се нарича още обмен с квитиране. Повечето съвременни шини осъществяват обмен, в който прилагат оптимална смес от принципите на синхронния и на асинхронния протокол.

Шини на “малкия” интерфейс

Кратко ще споменем шините, използвани в състава на така наречения “малък” интерфейс (вижте определението, свързано с фигура 5.5.1.2). Най разпространените шини от тази група са USB, FireWire, Bluetooth, IrDA. Някои от тях ще поясним в следващите раздели.

Шина

USB

Шината USB (Universal Serial Bus) се определя като

универсална последователна шина. Тя е предназначена за присъединяване на ниско

и средно скоростни външни устройства. Връзката се изгражда от 4 проводника. Два

от проводниците се използват за предаване и приемане на данни, а другите два

доставят захранване на външното устройство. Благодарение на това, някои външни

устройства може да нямат собствено захранващо устройство. Функционирането на USB системата се управлява от контролер, който е

програмно-апаратна подсистема на компютърната платформа. Към един контролер на USB шина могат да бъдат подключени до 127 външни устройства

чрез топологията “звезда”. В първата си версия (USB

1) шината осигурява две скорости на обмен - висока (до 12[Mb/s]) и ниска (1,5Mb/s]). Външните

устройства могат да имат различни скорости на обмен. Следващата версия на

стандарта (USB 2) предлага

скорост на обмен до 480[Mb/s]. Третата

версия – USB 3, обменя

данни със скорост от 4,8[Gb/s].

Известен е

вариант на USB шината

под наименованието Wireless USB,

позволяващ безжична връзка на разстояние до 3 метра със скорост 480[Mb/s], и на разстояние до 10 метра със скорост 110[Mb/s].

Шина

FireWire

Това е още

една стандартна технология за шина с последователен пренос на данни. Шината има 6 проводника, 4 от

които се използват за пренасяне на информация, а 2 са за захранване. Шината

осигурява висока скорост на предаване (до 800[Mb/s]

с перспектива до 3,2[Gb/s]).

Върху шината се поддържа режим на пакетно предаване на

данни. Данните се разбиват на пакети, а между пакетите се изпраща служебна

информация - команди “Стоп" или "Пуск". В асинхронен режим на

обмен всеки получен пакет се проверява и ако не е получен или е получен с

грешки, той се предава повторно. Използва се и изохронен режим, при който

пакетите се предават един след друг, без да се очаква потвърждение за

получаване.

Интерфейс Bluetooth

Bluetooth

означава “Син зъб”. Това е скандинавско наименование. Крал Harald Bluetooth,

водач на викингите, е известен като крал-обединител на скандинавските зами. С

това наименование конструкторите на този интерфейс вероятно са искали да

подчертаят "обединяващата" мисия на технологията. Основният елемент

на този интерфейс е приемо-предавателят, който работи с носеща честота 2,4[GHz]. Bluetooth-чипът, в зависимост от мощността,

позволява да се осъществи връзка на разстояние от 10 до 100 метра. В първите

версии скоростта на обмен е била в рамките на 2-3[Mb/s].

В стандарта Bluetooth

3.0 скоростта достига 480[Mb/s].

Предавателят

в този вид връзка разбива данните на пакети и ги предава на различни честоти.

Смяната на честотата се извършва 1600 пъти в секунда в случайна

последователност. Възможно е и предаване по шаблон от 79 честоти. Връзка

осъществяват само онези устройства, които са настроени на един и същи шаблон.

Интерфейс

IrDA

Инфрачервеният

интерфейс IrDA (Infra red Data Association)

позволява безкабелна връзка с помощта на ИК-излъчване с дължина на вълната 880[nm]. Портът на този интерфейс осъществява връзка на

разстояние до 1 метър в режим точка-точка. Преди предаване се формира кадър –

двоична комбинация от 10 бита, в която има един старт-бит, 8 бита данни и един

стоп-бит. Портът използва универсален асинхронен приемо-предавател UART, който предава със скорост от 2400 до 115200[b/s]. Преди началото на връзката устройството търси в

близкото обкръжение активност в ИК-диапазон. Ако се открие такова предаване,

предаването се отлага. Ако свързващите се устройства са компютри, всяко от тях

може да бъде водещо. Изборът прави онова устройство, което има първата инициатива.

В последствие устройства се договарят за параметрите на обмена. Целият първичен

обмен, свързан с договарянето, по подразбиране се осъществява със скорост 9,6[Kb/s]. Всяка една станция, не участваща в дадения обмен,

преди началото на предаването на данни, трябва да прослушва канала за връзка в

продължение на не по-малко от 500[ms],

за да се убеди, че липсва трафик в ИК-диапазон. От друга страна, станцията,

участваща в обмена, следва да предава данни в продължение на не повече от 500[ms].

Следващият

раздел е:

5.5.3 Съвременна

архитектура на входно-изходната система