Последната актуализация на този раздел е от 2020 година.

5.5.3.3 Архитектура

“Hyper Transport” на входно-изходната система

В търсене на висока производителност на

трансфера на данни за входно-изходната система, технологията, наричана сега Hyper

Transport - HT (хипер транспорт), се развива паралелно с

вече разгледаните от нас PCI Express и USB. И разбира се, подобно на техните

концепции, концепцията HT е също последователна – с основна цел замяна на

шинните съединения между периферните компоненти със система от двуточкови

двупосочни високо скоростни съединения. Нашата задача тук ще бъде да изложим

кратко особеностите на тази архитектура, на фона на останалите разгледани до

сега. Технологията HT е известна още под наименованието Lighting Data Transport.

Разработка е на компания AMD от 1997 година в качеството ѝ на

универсална технология за връзка между интегралните схеми в телекомуникациите,

в мрежовото оборудване, компютрите и вградените устройства, предоставяща висока

скорост и ниска цена. От 2004 година с разработката на стандарта на тази

технология се заема Hyper Transport Consortium. През следващата година AMD представи и процесорната

архитектура Hammer, с което изпревари за момента Intel.

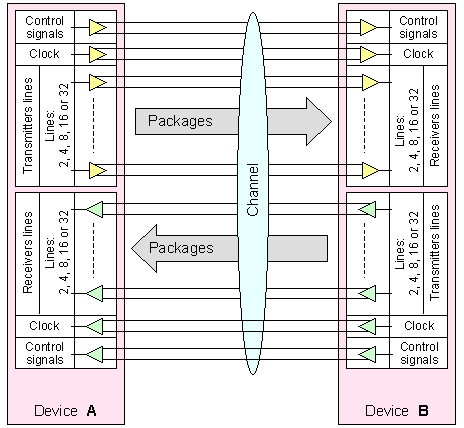

Hyper Transport е високоскоростна разширяема мултиплексируема шина с ниска латентност, с пакетно предаване на данни и комутируема верижна схема за свързване от тип “точка-точка" (Point-to-Point). Всеки интерфейс се състои от два еднопосочни канала, всеки с ширина 2, 4, 8, 16 или 32 [b] осигуряващ пропоскателна способност според следващата таблица. Последната, допълнена с данни за последните версии, се намира по-надолу.

|

|

Пропоскателна

способност [GiB/s] |

||

|

Ширина [b] |

200 [MHz] |

400 [MHz] |

800 [MHz] |

|

2 |

0,2 |

0,4 |

0,8 |

|

4 |

0,4 |

0,8 |

1,6 |

|

8 |

0,8 |

1,6 |

3,2 |

|

16 |

1,6 |

3,2 |

6,4 |

|

32 |

3,2 |

6,4 |

12,8 |

Данните се предават с нисковолтов диференциален сигнал с амплитуда 1,2[v]. Използва се външен

синхронизиращ сигнал в посока от източника към приемника. Честотата е каквато е

указана в горната таблица.

На следващата фигура е представена опростената структура на HT шината.

Фиг.

5.5.3.1.1. Организация на системна шина Hyper

Transport

Интерфейсът има 5-слойна структура,

следваща отблизо модела OSI (Open Systems

Interconnection Basic Reference Model). OSI е теоретичен модел, описващ принципен начин

на комуникация и строеж на телекомуникационни и компютърни мрежи. Като основна

градивна единица са използвани така наречените слоеве – всеки слой

предоставя интерфейс и услуги към по-горния слой, като в същото време получава

услуги от слоя под него. OSI моделът предоставя обща рамка, която производителите и

разпространителите да следват при проектиране на хардуера, операционните

системи и протоколите, като дефинира стандартните спецификации за комуникация

между системите. По-долу моделът ще бъде кратко пояснен.

Информацията,

изпращана по мрежата, е във вид на данни или пакети от данни. Ако например, два

сървъра (А и В) желаят да обменят информация, данните от предаващия А първо

трябва да бъдат снабдени със служебна информация относно транспорта им и

капсулирани (пакетирани). Информацията се предава от А към В, като при

преминаване през различните системи данните претърпяват промяна вследствие на

работата и функциите на отделните нива (слоеве). Приемащият сървър В приема

данните, като при него обработката на информацията се състои в премахване на

служебната информация, прибавена за целите на транспорта при изпращача.

Повече подробности читателят

може да разгледа в Интернет.

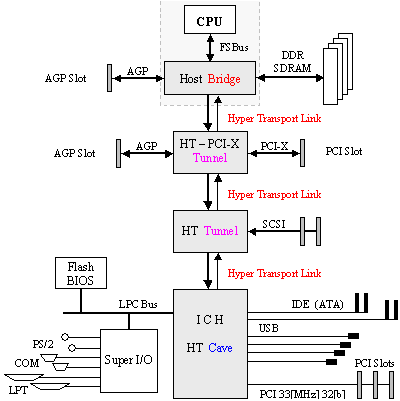

https://en.wikipedia.org/wiki/HyperTransport

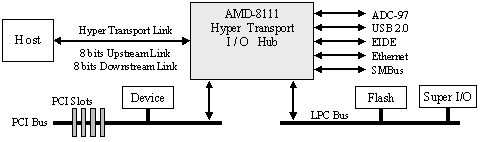

Високо скоростната шина Hyper Transport е предназначена да бъде използвана в компютърните системи преди всичко в качеството й на вътрешна локална шина. В сравнение с PCI шината, интерфейсът НТ позволява да се намали броят на проводниците върху системната платка, да се игнорира влиянието на закъсненията на сигналите, да се намали консумацията на ток и в цяло да се повиши пропускателната способност. Основната идея на НТ интерфейса е, както вече отбелязахме, да въведе нов тип съединение. Структурната схема на компютърна система с хипертранспортна архитектура на входно-изходната система е представена на следващата фигура.

Фиг. 5.5.3.3.2. Хипертранспортна архитектура

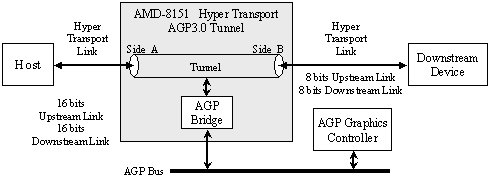

Главният мост, който може да бъде вграден в кристала на процесора, осигурява връзката на НТ с процесора (чрез Front Side Bus) и с паметта. Периферните контролери, които изискват висока скорост на обмен са реализирани като НТ-тунели. В края на връзката се намира входно-изходният хъб ICH, който се включва като краен елемент от тип “пещера” (HT Care). НТ архитектурата е проектирана така, че да може да осигури транзакциите от различни крайни интерфейси: PCI, PCI-X, AGP, USB и др. Транзакциите в архитектурата се изпълняват във вид на серии предавания на различни по формат пакети. Транзакциите съдържат адреса от паметта, кода на операцията (четене или запис), адреса на целевото устройство в конфигурационното пространство и вектора за прекъсване от контролера за прекъсване. В НТ архитектурата, за да се унифицират транзакциите, всички адресни пространства се проектират в едно общо пространство, което се адресира с 40-битов адрес, т.е. има обем 1[TiB]. Този адрес се предава в управляващите пакети. Началните 1012 гигабайта в пространството са заделени за отразяване на пространството на оперативната памет и за входно-изходната информация, отразена в паметта. В останалите 12 гигабайта се помества конфигурационното пространство (32[МiВ]), входно-изходното пространство (32[МiВ]), SMM-паметта, пространствата на адресите на векторите за прекъсване. Остават 54[МiВ], които се поддържат резервни.

НТ транзакциите осигуряват програмното взаимодействие на процесора с устройствата, прекия достъп до паметта и едноранговите взаимодействия на устройствата в конфигурационното пространство. Съществува и мрежова спецификация върху този интерфейс, която няма да коментираме тук.

Исторически НТ се разработва

от AMD като процесорна шина от последно поколение, съдържаща интегриран

контролер на паметта (архитектура AMD64). Това разбира се е следствие от

архитектурните решения за многопроцесорните системи на AMD, в които всеки

процесор контролира локална памет и освен това може да се обръща към паметта на

останалите. Тази архитектура е известна под наименованието NUMA (Non-Uniform Memory

Architecture). По това време (2000 година) шината се

наричала Lightning

Data Transport (LDT). НТ шината се проектирала като универсална много бърза

последователна шина, като за нея се предвиждали версии с намалена честота и

разрядност. Този подход за мащабиране “отгоре надолу” е различен от подхода за

мащабиране на PCI Express шината, която се мащабира “отдолу нагоре” – от х1 към

х16 и до х32. През 2001 година е основан консорциумът Hyper Transport

Consortium, поел задачата за развитие на НТ технологията. Към настоящият

момент имаме релийз №3.1, който е от 2008 година.

Следва да поясним, че понятието “последователна шина” съвсем не определя за нея еднобитова ширина. Много по-важно е да се разбира, че паралелните шини са твърдо свързани със своята физическа реализация, а последователните предават всякакви данни във формата на последователни пакети, но в някаква абстрактна физическа среда. По тази причина НТ шината (с минимална ширина 2 бита) с пълно право се нарича последователна – всякакви данни, предавани по нея, са опаковани в пакети, имащи стандартен вид.

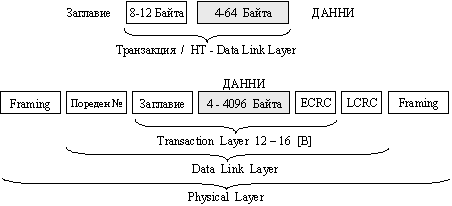

Както отбелязахме в началото, на подобие на много други съвременни интерфейси и НТ има многослойна организация в съответствие с модела OSI:

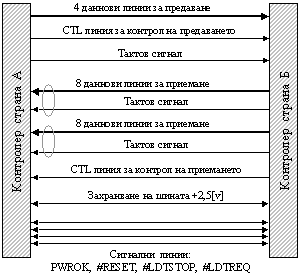

1. Съставът на физическия слой е представен на следващата фигура:

Фиг. 5.5.3.3.3. Състав на шина Hyper Transport

Както се вижда, предвидено е само съединение от тип точка-точка, двупосочно разделно, в което се използва диференциална сигнална двойка (с нива на напрежението +1,7[v] и -0,3[v]), с импеданс 100[W] и вградени в контролерите терминатори на шината. Възможно е използването на 2, 4, 8, 16 или 32 линии във всяко направление (всяка линия представлява 2 усукани проводника), при това ширината на отделните направления може да бъде различна (например, разрешава се да се използват 2 линии за приемане и 32 за предаване). Сигналните линии са: PWROK – признак за стабилност на захранването и синхронизацията; RESET# – сигнал за начално установяване на устройствата във веригата; LDTSTOP# – сигнал за разрешение/забрана за използване на съединения при смяна в състоянието на системата; LDTREQ# – индикатор за активност на съединението или за заявка на устройството. Тези сигнали са бавни – формират се от изходен транзистор с отворен сток (open drain), като се обединяват в обща точка, формирайки логическата функция “монтажно ИЛИ”. Към състава на физическото ниво следва да се причислят и хардуерните контролери в крайните точки на свързване, чиято логическа структура и алгоритми на функциониране няма да разглеждаме.

Данните се предават по традиционната DDR (Double Data Rate) схема по преден и по заден фронт на тактовия импулс. Технологията за предаване по двата фронта на синхронизиращия импулс е изложена в раздел 4.2.2 на тази книга. Графично DDR същността е пояснена на фигура 4.2.2.15. За предаване и за приемане има отделни и независими тактови сигнали. Ако ширината на даденото направление превишава 8 бита, то тактуващите линии са повече от една (за всеки 8 бита отделна линия). Захранващата линия от 2,5[v] е само за нуждите на самата шина – всички останали НТ-устройства се захранват автономно.

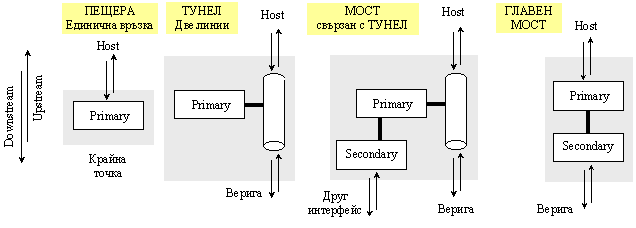

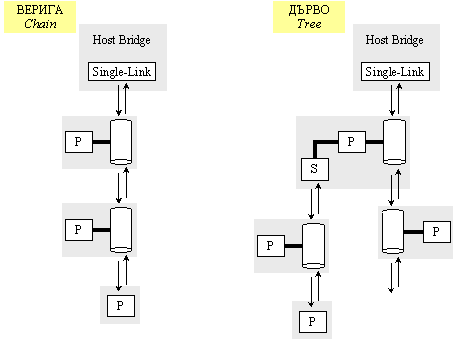

Физическите устройства в рамките на НТ интерфейса се разделят на следните типове (вижте следващата фигура):

· Устройство “пещера” (Cave). Крайно устройство в един двупосочен НТ канал за връзка (използва се само за вход) ;

· Устройство “тунел” (Tunnel). Устройството има два НТ интерфейса в двупосочен канал за връзка, реализиращо “проход” (но не мост). Такива устройства могат да се подреждат във верига (daisy chain), която да образува логическа шина. Веригата следва да се подключи към процесора (чрез главния мост), който поддържа конфигурацията и управлява работата на хипер транспорта. В една верига могат да бъдат свързани до 32 устройства, като се брои и мостът ;

· Устройство “мост” (Bridge). Това е устройство, разполагащо с два интерфейса. Единият от тях е първичен и е насочен към главния мост (Host Bridge). Това устройство образува двупосочен канал за връзка, в който единият от каналите се приема за главен и свързва устройството с контролер на шина (Host), а другият се свързва с други вторични устройства. Мостът има набор от регистри, съдържащи информация за цялостното движение на транзакциите между тези шини.

Собственик на шината е главният мост, който изпълнява функциите по конфигуриране. Основният вариант на топологията на шината е верига от устройства-тунели. Всеки НТ интерфейс се състои от две независими части – предавател и приемник. При конфигуриране за всяко устройство се назначава отделна област в адресното пространство. Във веригата от тунели транзакциите се разпространяват низходящо и възходящо. Ако в низходящ управляващ пакет дадено устройство разпознае своя адрес, то разбира, че следващата по шината информация е предназначена за него (управляващи пакети и данни). Възходящият трафик тунелите прехвърлят без да се интересуват от съдържанието му. В отговор на получените заявки устройството изпраща възходящо пакети, като ги включва по подходящ начин във възходящия трафик. По този начин се осигурява програмното взаимодействие на процесора с устройствата. Своите собствени заявки за достъп до паметта устройството изпраща също нагоре по шината, както и заявки (обръщения) към други устройства, независимо от тяхното разположение по веригата относно него самото. Доставката на пакета до адресата осигурява главният мост: той обръща посоката на пакета, като го изпраща надолу по веригата до адресата. На пакет, който е адресиран до оперативната памет, главният мост организира отговор от контролера на паметта, реализирайки по този начин пряк достъп до паметта. Възможни са и други по-сложни топологии, например топология дърво.

Физическото свързване на периферни устройства към НТ-шината може да става по няколко начина. Процесорът е винаги главно устройство (Host). Ако към него има свързано само едно единствено устройство, тази конфигурация се определя като “пещера” (Cave). Тази конфигурация обаче е изключение, тъй като интерфейсът НТ е предназначен да свързва повече на брой устройства. Някои видове конфигуриране на подчинени устройства са показани по-долу.

Фиг. 5.5.3.3.4. Свързване на подчинени устройства

Възможно е голямо разнообразие от конфигурации, изпълнени с трите вида устройства – пещера, тунел и мост.

Фиг. 5.5.3.3.5. Топология “Верига” и “Дърво”

Основното предимство на верижната структура е възможността да се опрости системният дизайн. НТ е интерфейс, който е създаден с идеята да бъде изцяло съвместим с PCI архитектурата, да използва същата семантика на регистрите, същите конвенции за конфигуриране на устройствата (Plug&Play) и същите методи за изграждане на мостове към други интерфейси. Това максимално подпомага софтуера, тъй като архитектурата е напълно прозрачна за операционната система.

“Базовата” тактова честота на шината е 200[MHz], което в смисъла на схемата DDR означава, че предаването на данни е с честота 400[MHz]. Това е минимално възможната честота за функциониране на шината и тя определя минималната пропускателна способност на НТ-връзката, т.е. при 2 бита минимална ширина се получава скорост от 100[MB/s]. За разлика от PCI-E, в която кодирането “8/10” “изяжда” около 20% от времето, тук тази оценка е пълноценна. Всички следващи честоти се определят като кратни – 400[MHz], 600[MHz], 800[MHz] за Hyper Trasport 1.0 и 1.1, 1000[MHz], 1200[MHz] и 1400[MHz] за последните версии. Съответните скорости са представени в таблицата.

Таблица 5.5.3.3.1 Скорости на трансфер

|

Честота [MHz] |

2 бита [MB/s] |

4 бита [MB/s] |

8 бита [MB/s] |

16 бита [MB/s] |

32 бита [MB/s] |

|

200 |

100 |

200 |

400 |

800 |

1600 |

|

400 |

200 |

400 |

800 |

1600 |

3200 |

|

600 |

300 |

600 |

1200 |

2400 |

4800 |

|

800 |

400 |

800 |

1600 |

3200 |

6400 |

|

1000 |

500 |

1000 |

2000 |

4000 |

8000 |

|

1200 |

600 |

1200 |

2400 |

4800 |

9600 |

|

1400 |

700 |

1400 |

2800 |

5600 |

11200 |

От таблицата например се вижда, че даже за минималната ширина (2+2 бита, 21 проводника, 400[MB/s]) 800 мегахерцовата НТ шина позволява получаването на производителност, която е двойно по-голяма от тази на PCI Express x1 (1+1 бита, 36 контакта в слота, 250[MB/s]). Производителността на “старшите” версии на НТ (32 бита) съответства по скорост на двуканална памет DDR400. Следващата стъпка дава производителност на два канала DDR500, а НТ 2.0 е принципно способна да осигури предаването на данни от двуканална DDR2-800. Този широк спектър от скорости удовлетворява и най-разнообразните приложения – от прости до високо производителни. Така НТ технологията е реален конкурент на последното предложение на Intel за PCI Express.

2. В логическия слой се определя редът за инициализация и конфигурирането на устройствата, установяването и прекратяването на сеансите за връзка, изчислява се контролната сума за данните, отделят се пакетите за предаване на данни.

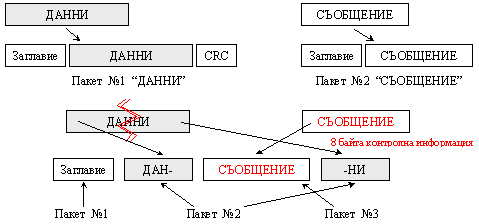

Хипер транспортът тук е организиран доста необичайно за пакетните системи – оказва влияние физическото ниво. Цялата информация за предаване ясно се отделя на служебна и на непосредствени данни. За това разграничаване е предназначена линията CTL. НТ пакетът е само порция данни, която има определен формат. В първия пакет ще бъде предадена цялата служебна информация, а във втория (веднага след първия) ще се намират данните – без всякакви заглавия. За минимизиране на задръжките е разработена технологията за усъвършенствано обслужване на заявките (PRI – Priority Request Interleaving). Това е апаратно вграден механизъм, който следи приоритетите на заявките, минаващи по шината. При това в момент на предаването на данновия пакет на устройството може да му се наложи да изпрати спешно също такава информация (някакъв системен пакет). Тогава е прието предаването на първия пакет данни ще бъде прекъснато за да бъде изпратен служебният пакет, след което се възобновява предаването на прекъснатият пакет с данни.

Фиг. 5.5.3.3.6. Схема на прекъсването PRI

Тази схема е необходима за да се осигурят минимални задръжки при предаване на съобщенията – при достатъчно широка шина типичната задръжка при предаване на съобщения в НТ е в границите на 1 или 2 такта. Подобни задръжки определят латентността на контролера на паметта на “отдалечен” процесор. Това се дължи на малкия обем управляваща информация в пакетите – в сравнение с другите интерфейси, НТ използва най-късите заглавия с такава информация: 8 байта при операция четене (управляващ пакет със заявка за четене на конкретни данни, след което следва пакета с желаните данни); 12 байта при операция запис (8 байта е съдържанието на управляващия пакет със заявката за запис, 4 байта са управляващ пакет с отговор на заявката, след което следва пакета с данните). Операция запис по НТ шината се изпълнява по два начина, които се наричат posted и non-posted. Posted-операцията запис се състои в предаването на единствен пакет, който съдържа адреса за запис и самите данни. Тази операциия обикновено се използва за обмен на данни с високо скоростните устройства чрез канал за пряк достъп до паметта.

Non-posted операцията запис представлява изпращане на два пакета: устройството, инициирало операцията запис, изпраща към устройството получател пакет, който съдържа адрес и данни. Устройството получател, получавайки такъв пакет, изпълнява операция запис и изпраща обратно към устройството инициатор пакет, който съдържа информация за това дали е била успешно изпълнена операцията запис. По този начин posted-записът позволява да се постигне максимална скорост за предаване на данни (няма загубено време за прехвърляне на потвърждаващи пакети), а non-posted-записът осигурява по-надеждно предаване, разчитайки на пакета отговор.

На следващата фигура са дадени за сравнение пакетите при PCI Express и HT интерфейс. Лесно се забелязва значително по-лекия НТ пакет.

Фиг. 5.5.3.3.7. Формати на пакетите в HT и PCI Express интерфейси

И още нещо характерно за НТ протоколите – формирането на контролните суми. “Нарязаният” на парчета поток от данни получава контролна сума за всяко парче, който се вклинява в потока. В действителност се вклинява 4-тактен интервал, в който се предава CRC на предидущия пакет.

3. Нивото на протокола са определени командите в съобщенията, които формират виртуални канали за връзка. Тук са определени и правилата за управление на потоците.

4. Нивото на транзакциите са конкретизирани управляващите сигнали при четене или при запис.

5. Нивото на сесиите съдържа правилата за управление на консумацията на енергия и други команди с общ характер.

Топологията на устройствата върху НТ шината може да бъде построена във вид на верига или дърво. Фирмата AMD предлага готови интегрални схеми, поддържащи тази шина: схемата AMD-8151 е тунел “HT - AGP”; AMD-8111 е хъб за входно-изходни канали, а AMD-8131 е тунел “HT - PCI-X”. Така се осигурява съвместимост с други, дори морално остарели интерфейси от една страна, а от друга – плавен преход към новите. В минималната конфигурация НТ шината има 24 контакта – 8 за данни + 4 за тактови сигнали +4 линии за управление + 2 сигнални + 4 заземявания + 1 захранване + 1 ресет. В максимална конфигурация (ширина на канала 32 бита) линиите са общо 197. Ето някои конфигурации с тези схеми:

Фиг. 5.5.3.3.8. Възможности на AMD-8151 (HT-AGP-тунел)

Фиг. 5.5.3.3.9. Структура с AMD-8111 (HT I/O Hub)

На физическо ниво технологията НТ използва подобрена версия на ниско волтови диференциални сигнали със съпротивление 100[W]. Нивото на сигнала е 1,2[v]. Всичко това позволява шината да достига дължина около 61 сантиметра и скорост от 800[Mb/s] на една линия. Разделените низходящи и възходящи потоци позволяват повишена тактова честота. Пакетът включващ адреса, командата и данните е винаги кратен по дължина на 32.

Най-новата версия НТ 3.1 поддържа:

· Тактова честота до 3,2[GHz] за ядрото на процесора, при което скоростта за трансфер на данни в едната посока достига 25,6[GiB/s] ;

· Включване и изключване на крайни устройства “в режим на експлоатация” Hot plug ;

· Динамично конфигуриране (например 1х16 НТ ще може виртуално да се преконфигурира в 2х8 НТ, което е полезно за 2 ядрените процесори ;

· Нови подобрения и в силовата част Power Management, които водят до увеличаване на отдалечеността – до повече от 1 метър. Това е хардуерна динамична поддръжка на промени в тактовата честота и ширината на шината ;

· DC/AC авто-конфигурация. Апаратурата следи за наличието на висока стойност на капацитета на преносната мрежа и ако се открият кондензатори, шината автоматично бива превключвана в променливотоков режим на работа. Ниски стойности на капацитета се интерпретират като къси връзки, а обратното – като дълги.

За сега в предлаганите от водещите производители чипсети не се наблюдава използване на Hyper Transport технологията в качеството й на универсална транспортна структура. Все пак тази шина е широко застъпена, като се използва не само в обикновените компютърни платформи, но в сървъри, клъстери, мрежово оборудване, конзоли и пр. устройства. Бъдещето ще покаже възможностите й да се наложи в конкурентните условия на останалите технологии.

Следващият

раздел е:

Глава 6. ОРГАНИЗАЦИЯ НА

ЗАПОМНЯЩАТА СИСТЕМА