Този

раздел е нов.

Създаден е

през 2023

година.

6.3.2.1.2.

Етапи в

протокола за

обслужване

на първичната

кеш памет

От

гледна точка

на процесора,

единствените

операции

(команди),

които имат

отношение

към кеш паметите

са LOAD и STORE. Първата

команда заповядва

доставка на

данни от кеш

паметта, заявени

от процесора,

при което ги

зарежда в

регистър от

регистровата

му памет а

втората,

обратно –

прехвърля

данни от

регистър на

процесора

като ги

записва в кеш

паметта. Вече

изяснихме в

предходните

раздели същността

на процесите,

свързани с

движението на

данните

между

отделните

нива в

йерархията

на

запомнящата

система и

читателят навярно

се е убедил

във високата

алгоритмична

сложност на

това

движение

(вижте раздел

6.3.2).

Сложността

се обуславя

от

многообразието

на

състоянието,

в което могат

да бъдат заварени

отделните

нива на

запомнящата

система, при

изпълнение

на тези

операции,

както и от

разнообразието

на нейната

логическа структура.

Ние

отново ще се

постараем да

осветлим тези

така сложни

процеси. Може

би най-сложната

ситуация

настъпва в

кеш памет, която

използва

стратегията

“с обратен

запис". Тук ще

препоръчаме

на читателя,

ако е възможно,

да работи

съвместно с раздел 6.3.2.1,

като обърне

особено

внимание на

поясненията

към фигура

6.3.2.9 и фигура

6.3.2.10. В този

случай кеш

паметта

трябва да

работи както

с

попаденията (hits), така и с

пропуските (misses) при

асоциативното

претърсване

на справочника.

За това какво

е на

асоциативното

претърсване

(асоциативен

достъп),

читателят може

да изучи като

се запознае с

методите за

достъп в

различните

видове устройства

за запомняне,

които са

изложени в глава 4 на

тази книга. В

стратегията

с обратен

запис се

използва протокол,

чиито етапи

имат

следните

наименования:

·

Load hit ;

·

Clean load miss ;

·

Dirty load miss ;

·

Store hit ;

·

Clean store miss ;

·

Dirty store miss .

В този

кратък

раздел ще

разгледаме

действията

във

върховата

степен на

йерархичната

запомняща

система, за

да бъдем

максимално

полезни на

читателя, в

желанието му

да изясни за

себе си тази

толкова

сложна,

многоуровнева

и знàчима

част от

логическата

структура на съвременните

компютърни

системи.

1.

Етап

на протокола Load Hit

Този

етап се

налага да

бъде

изпълнен,

когато

процесорът

иска да чете

данни от

адрес, които

се съдържат в

блок от кеш

паметта. Това

се случва,

когато в

резултат на

асоциативното

претърсване

на

справочника

с формирания

от адреса

таг, се

открива

необходимия

блок. В

резултат на сравнението

се генерира

сигнал за

съвпадение (hit). Този

сигнал

инициира в

контролера

на кеш паметта

изпълнението

на онзи етап

от протокола,

който

поясняваме в

този пункт.

Ситуацията е

една от

ней-елементарните

– следва

отваряне на

“улучения” в

данновия

масив блок и

процесорът

получава

данните по

заявения

адрес. Това е

илюстрирано

със следващата

рисунка.

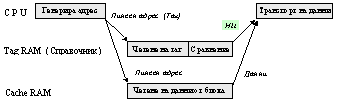

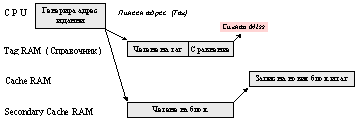

Фиг.

6.3.2.1.2.1. Схема

на етапа Load hit

От

линейния

адрес, който

процесорът е

формирал, се

отделят

структурните

елементи, необходими

за достъп в

кеш паметта.

Контролерът

на кеш

паметта

издава

достъпните

по адреса

данни от

отворения

блок и

задейства трансфера

им по

данновата

шина. Освен това

той

отбелязва

обръщението

към дадения

блок, като

потвърждава

или повишава

оценката за

неговата

активност в

управляващото

му поле

(вижте фигура

6.3.2.3).

2.

Етап

на протокола Clean Load Miss

Ако

след

асоциативното

претърсване

на

справочника

с подадения

от процесора

таг, се

установи

липса на

търсените данни

в кеш

паметта, то

се генерира

сигнал за

несъвпадение

(Miss). В този

случай

контролерът

на кеш

паметта следва

да достави

исканите

данни от

по-ниските

нива на кеш

паметта.

Тук

настъпват

няколко

възможности.

На първо

място трябва

да се намери

свободен

(празен,

неактуален)

блок в кеш

паметта,

където да се

поставят

данните,

които

контролерът

ще достави от

по-ниското

ниво. Ако се

намери свободен

блок,

доставените

данни ще бъдат

поставени

(записани) в

него. След

това процесът

се развива

според

схемата на

предходния

етап на

протокола.

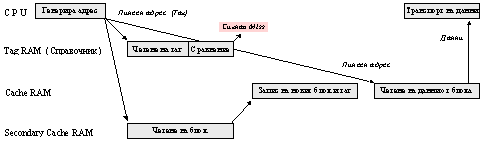

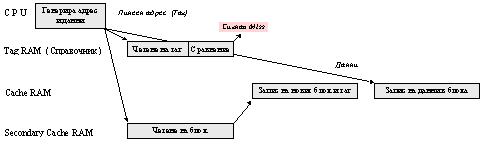

Фиг.

6.3.2.1.2.2. Схема

на етапа Clean Load Miss

Ще

припомним, че

състоянието

на даден блок

в кеш паметта

се определя

от

управляващото

поле на

блока. Съдържанието

на това поле

се определя

от контролера

на кеш

паметта и се

актуализира

след всяко

обръщение

към него,

така че след

записа,

блокът вече

не може да се

определя

като свободен.

3.

Етап

на протокола Dirty Load Miss

В

случай че

контролерът

на кеш

паметта не намери

свободен

блок за

новите данни,

тогава се

налага да се

освободи

такъв. Преди

това обаче се

налага да

бъде избран

блокът, който

предстои да

бъде

освободен

(опразнен).

Процедурата

се нарича “избор

на кандидат

за

изхвърляне",

пояснена в

предходния раздел 6.3.2.

Тук за

контролера

възниква

нова дилема.

За да се

освободи

блок, не е

възможно

данните в

него да бъдат

просто

изтрити.

Както

вече знаем от

предходния

раздел, данните

в кеш паметта

са копия от

съдържащите

се такива в

по-ниските

нива на

паметта. В процеса

на

обработката

им обаче

процесорът модифицира

тези данни.

Така данните

в първичната

кеш памет е

възможно към

този момент

вече да не

съвпадат с

тези, чието

копие са били

първоначално.

Така,

налагащото

се освобождаване

на блок в кеш

паметта

изисква модифицираните

в него данни

да бъдат да

бъдат

изхвърлени с

актуализация

на всички негови

копия,

съдържащи се

в по-ниските

нива на

паметта, чак

до основната

памет.

Актуализацията

е всъщност

запис на

обновените

данни върху

старите им

варианти.

След

като по този

начин

съответният

блок в кеш

паметта бъде

маркиран

като

свободен, с подадения

от процесора

адрес,

спускайки се

в низходящ

ред по

йерархията

на запомнящата

система, се

достъпват

необходимите

му данни.

Издигайки се

обратно, в

посока към

процесора,

тази данни

заемат

последно

освободения

в първичната

кеш памет

блок, който

след това се

маркира в

управляващото

поле вече

като активен.

След това, в

съответствие

с адреса,

подаван от

процесора, от

така

доставения

блок, към

него се

изпращат

точно

исканите

данни. Последователните

действия на

протокола са

илюстрирани

на

следващата

рисунка.

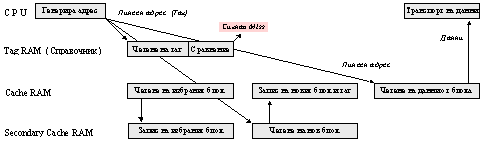

Фиг.

6.3.2.1.2.3. Схема

на етапа Dirty Load Miss

Етапът

на протокола Dirty load miss е

известен още

под наименованието

Load copyback.

4.

Етап

на протокола Store Hit

Този

етап на

протокола се

изпълнява в

кеш паметта,

когато

процесорът

иска да

запише изчислен

от него

резултат. За

целта той

издава

адреса за

запис, чийто

таг попада в

първичната

кеш памет.

Последната

извършва

асоциативно

търсене и ако

бъде

намерено

съвпадение,

се генерира

сигнал Hit. При

това,

контролерът

извършва

запис на подаваните

от процесора

данни в така

достъпения

блок. В

повечето

случаи с това

се извършва

модификация

(актуализация)

на данните,

съдържащи се

до този

момент в

съответното място

на кеш

паметта.

Освен това

контролерът

отбелязва

това

обръщение,

като потвърждава

или повишава

оценката за

активността

на

достъпения

блок.

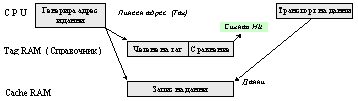

Фиг.

6.3.2.1.2.4. Схема

на етапа Store Hit

5.

Етап

на протокола Clean Store Miss

При

операция STORE (запис),

освен горе описаната

ситуация, е

възможна и

противоположната,

при която в

резултат на

асоциативното

претърсване

на

справочника

не се открива

подавания

таг. В

резултат на

това в кеш

паметта се

генерира

сигнал Miss.

Ситуацията

се обяснява с

това, че в кеш

паметта не се

съдържа

търсеният

блок, който

или е бил

изхвърлен

след загуба

на активност,

или не е бил

зареждан до

момента.

Естествено

данните,

които

процесорът

иска да

запише, не

могат да

бъдат

загубени –

това е

недопустимо.

Логиката ни

подсказва, че

следва да се

действа аналогично

на протокола Clean store miss. С

други думи, в

кеш паметта

следва да се

намери

свободен

блок, в който

да се достави

копие на

данните,

чийто адрес

процесорът е заявил.

Когато

копието на

тези данни

постъпи в кеш

паметта,

тогава ще се

изпълни и операция

STORE, с

което ще бъде

извършена

актуализация

(модификация)

на тези

данни.

Описваният

в този пункт

етап на

протокола, контролерът

на кеш

паметта

изпълнява,

решавайки

задачата за

намиране и

освобождаване

на блок.

Намирането

на блок

“кандидат за

изхвърляне"

се извършва

след анализ

на признаците

в

управляващите

полета на

отделните

блокове в кеш

паметта. В

предходния

раздел са

описани

няколко

известни

стратегии за

избор на

кандидат за

изхвърляне – RC, LFU, LRU, FIFO и

техни

разновидности.

Без

освобождаване

на място в

кеш паметта

не могат да

се изпълнят

действията,

които са

необходими, за да

завърши

успешно

операция STORE.

С помощта

на подадения

от процесора

адрес в по-ниските

нива на

паметта,

включително

до основната,

се търси

достъп до

необходимия

блок, Той се

прочита и

неговото

копие се

изкачва по

йерархията

на

запомнящата

система, достигайки

първичната

кеш памет,

където се записва

в избрания

свободен

блок. С това

завършва

подготвителната

част от

действията,

свързани със

записа, който

процесорът

иска да

извърши.

Фиг.

6.3.2.1.2.5. Схема

на етапа Clean Store Miss

6.

Етап

на протокола Dirty Store Miss

При

опит за

запис, след

установяване

на несъвпадение

(сигнал Miss) и след

изпълнение

на етапа Clean store miss, с

подадения

таг,

контролерът

на кеш паметта

търси

съответния

нов блок във

вторичната

кеш памет.

Ако го

намери, той

го прочита и

го “издига"

нагоре, за да

го запише в

освободения

блок на първичната

кеш памет.

Заедно с

данните, в освободеното

преди това

място се

записва и новия

таг и

признаците в

управляващото

му поле. С

това става

възможно

следващото

изпълнение

на заявената

от процесора

операция STORE. Тя

изисква

запис на

изпращаните

от него

данни, което

става в така

подготвения

вече блок в

кеш паметта.

С това

данните в

блока се

актуализират

(модифицират),

т.е. блокът вече

не е чисто

копие.

Фиг.

6.3.2.1.2.6. Схема

на етапа Dirty Store Miss

Заключение

Вече

изяснихме в

предходните

раздели на

тази книга

същността на

процесите,

свързани с

движението

на данните по

отделните

нива в йерархията

на

запомнящата

система и

читателят навярно

се е убедил

във високата

алгоритмична

сложност на

това

движение

(вижте раздел

6.3.2).

Сложността

се обуславя

на първо

място от

многообразието

на

състоянието,

в което могат

да бъдат

заварени

отделните нива

на

запомнящата

система при

изпълнение

на тези

операции, а

на второ

място – от

многообразието

на методите

за адресиране

в

справочника на

кеш паметта.

Последното е

пояснено

подробно в раздел 6.3.2.1.

След

просторните

обяснение за

ролята, мястото

и

предназначението

на кеш

паметта в цяла

поредица от

раздели сме

убедени, че

читателят

вече е наясно

със

значението

на тази памет

относно

повишаването

на

производителността

на компютърните

изчисления.

Но все още

нищо не сме

казали

относно

производителността

на самата кеш

памет, освен

това, че тя се

изпълнява в елементната

база на самия

процесор и в

непосредствена

близост, при

минимална

дължина на свързващите

линии. Това

обаче не са

единствените

способи за

повишаване

на производителността

на самата кеш

памет.

Многократно

в нашите

книги и в

много от нашите

статии и

доклади сме

писали за

различни

форми на

паралелизъм

при

организиране

на

изчисленията,

при това

както на

хардуерно,

така и на

софтуерно

ниво.

Главната цел

на

паралелизмите

е именно

повишаването

на

производителността

на системите.

Ето защо не

можем да подминем

тези форми за

организация

и в самата кеш

памет, където

те също имат

място.

Разбира се,

далече сме от

желанието да

изложим темата

изчерпателно,

затова ще

споменем

само един

пример,

колкото да

провокираме

читателя към

самостоятелни

му

изследвания.

Например,

след сигнал

за

несъвпадение

Miss

при

асоциативното

претърсване

на справочника,

контролерът

на кеш

паметта

следва да

достави търсения

блок от

вторичната

кеш памет или

даже от

основната.

Паралелно с

това обаче, докато

той работи с

по-ниските

нива на паметта

и

осъществява

доставката

на новия блок

данни, в

справочника

той може да

запише тага

на новия

блок, който

се съдържа в

линейния

адрес,

подаван от

процесора. В

протоколите за

функциониране

на кеш

паметта, на

които се

спряхме по

горе, има и

други

възможности

за паралелни

действия.

Всичко това

обаче е твърде

конкретно и

излиза извън

рамките на

нашите цели

тук.

Следващият

раздел е:

6.3.2.2.

Кохерентност

на кеш

паметта. Протокол MESI