Последната

актуализация

на този

раздел е от 2021 година.

6.4.3

Сегментна

организация

на паметта

Изложеното

в този раздел

има много

общо с изложеното

в

предходните

раздели, ето

защо то ги

допълва в

голяма

степен.

Разделянето е

твърде

условно и е

направено

единствено с

желанието да

улесни Читателя

при

изучаване на

темите.

Сегментната

организация на

адресното

пространство

вече беше

определена

като втори

основен вид

организация,

при който размерът

на

структурните

единици е

променлив и

когато той се

определя по

някакво

логическо

правило. Сегментната

организация

в

исторически

план се е

появила

първа, във връзка

с

невъзможността

една

сравнително

голяма

машинна

програма да

се помести изцяло

(в пълния си

обем) в

оперативната

памет, която

по онова

време е била

с твърде

скромен обем.

Програмистът

е бил длъжен

да извърши

сегментиране

на своята програма,

като я разбие

на отделни

логически свързани

части. Ще

припомним, че

алтернативната

странична

организация

на паметта се

поддържа

извън волята

на

програмиста,

с програмни и

апаратни

средства. При

изпълнение на

програмата

отделните

сегменти

трябвало да

се зареждат

при

необходимост

в оперативната

памет. За

това

естествено

трябвало да

се грижи

програмистът.

В резултат,

употребените

от

програмиста

адреси при

написване на

програмата,

получават

абстрактен

характер. В

същото време,

във

физическата

памет се получава

така, че

различни

команди на

програмата,

имащи

различни

логически

номера в командната

последователност,

при изпълнение,

попадат в

клетки с едни

и същи

физически

адреси,

откъдето

могат да

правят

обръщение също

към едни и

същи

физически

адреси. Това

естествено е

възможно

само в

различни

моменти от

времето.

Сегментите

на

програмата

по своята

логическа

същност имат

различна

дължина и

заемат

различен

обем от

основната памет,

но не повече

от

максимално

възможния. Сегмент,

това е

програмна

(логическа)

единица, като

например

главна

програма,

подпрограма,

масив от

данни, или

част от масив

от данни. Тъй

като

дължините на

сегментите

предварително

не са

известни, то

удобно е, програмистът

да въведе за

всеки

сегмент една

и съща

номерация на

клетките,

започвайки от

нула.

Сегментирането

на

програмното

осигуряване

може да се

изпълни

ръчно, по

време на програмирането

чрез

въвеждане на

специални

указатели в

програмата,

или

автоматично

при

транслиране

на

програмата

от изходния

език на

машинен език,

или още чрез

апаратно-програмни

средства по

време на

изпълнение

на

програмата. Както

вероятно

читателят се

е убедил от

предидущия

пункт,

генерално

управлението

на паметта на

компютърната

система се

ръководи от

различни

програмни

елементи,

които са

съставна

част на

операционната

система,

която не е

обект на

нашето внимание.

По тази

причина тук

отново ще се

задоволим с

изложение

най-вече на

необходимите

апаратни

технически

решения,

осигуряващи

този вид

организация.

Както

следва от

концепцията

за виртуална памет,

потребителската

програма не

прави разлика

между

основната и

виртуалната

памети, като

адресира

необходимите

ѝ клетки, като

че ли

всичките те

се намират в

основната

памет. В

действителност,

процесорът

може да се

обръща

непосредствено

само към

основната

памет, в

която в различни

моменти от

времето

операционната

система

зарежда за

него

различни

сегменти. Този

процес

следва да

бъде напълно

независим от

програмиста,

ето защо

всички

методи за преобразуване

на

виртуалните

адреси се основават

на

апаратни и

апаратно-програмни

средства.

Общата

структура на

виртуалния

адрес остава

същата, като

беше

илюстрирана

на фигура

6.4.1. Що

се отнася до

структурата

на

виртуалния линеен

адрес, според

казаното до

момента, се

стига до

извода, че

при сегментна

организация

на адресното

пространство,

тя трябва да

се състои от

следните две

части:

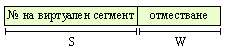

които

формират

общата му

дължина Lv = S+W. В

горната

рисунка се

приема, че

отместването

е стойност,

която се конкатенира

с номера на

сегмента, т.е. S+W=S|W.

Когато

се посочи

дадена

клетка чрез

комбинацията Аddr=<S,W>, това

означава, че

тя се намира

в сегмент с номер

S

и отстояща на

D

клетки от

неговото

начало, което

практически

означава, че

в рамките на

даден

сегмент ще се

прилага

относително

адресиране

спрямо

началния, или

още базовия

адрес на този

сегмент. По-горе

с буква D

е означена

стойността

на

отместването.

Според

горната

структура,

всеки

програмист

приема, че

разполага с M, ( M=2S ) на

брой

виртуални

сегменти,

всеки от

които има

максимален

обем от Q, ( Q=2W

) на

брой клетки (където

S и W са

посочените в

рисунката

по-горе

дължини).

Тези

сегменти

запълват

цялото

адресно пространство,

като се

конкатенират,

т.е. областите,

които те

заемат не се

застъпват (не

се

припокриват).

Когато адресното

пространство

се използува

от няколко

програмиста

(или от

няколко

отделни задачи),

всеки от тях

може да счита

например нулевия

сегмент за

свободен и

изцяло свой и

да приема, че

неговата

програма ще

се разполага

там. По тази

логика,

втория и

третия сегмент

той може да

определи

примерно за

стек, за

поместване

на изходните

данни и на

резултатите.

Същото

разпределение

на виртуалното

адресно

пространство

могат да

направят и

останалите

програмисти.

Когато

операционната

система

приема

отделните

задания за

изпълнение,

тя не може да

разположи в

един и същи

физически

сегмент

няколко

програмни

сегмента (с

техните

виртуални

адреси), тъй

като

адресното

пространство

е едно. Ето защо,

отделните

потребителски

сегменти се разполагат

последователно

един след

друг, без

припокриване,

при което

следва

задължително

да се опише еднозначното

съответствие

между

номерата на

заданията и

номерата на потребителските

сегменти.

Например,

програмните

сегменти на

първия

потребител

могат да бъдат

с номера 0, 1 и 2;

на втория

отново 0, 1 и 2; на

третия също 0, 1

и 2. Ако и трите

процеса са

заредени в

оперативната

памет,

съответните

виртуални

сегменти ще

бъдат

разпределени

в 6 различни

физически

сегмента.

Съответствието,

което трябва

да се фиксира

и води на

отчет, следва

да се опише само

чрез

запомнянето

му в

специална,

нарочно

създадена

таблица на

съответствието.

Създаването

и

поддържането

на тази таблица

на

съответствието

е задача на

операционната

система. В

тази таблица,

всяко прието за

изпълнение

задание, се

номерира (0, 1, 2, ...),

а всеки негов

програмен

сегмент, се

измерва.

Всеки ред от

сегментната

таблица се

нарича

описател (дескриптор)

на физически

сегмент и

съдържанието

му служи за

реализация

на

съответствието.

Максималният

брой

сегменти, с

които може да

разполага

всеки

програмист е M,

следователно

всяко

задание ще

описва предназначението

и реалния

обем на тези

потребителски

сегменти, в

една сегментна

таблица, а

описанието

кое задание в

коя

сегментна таблица

се намира,

поддържа

операционната

система, в

своята

таблица на

заданията.

При

това

структуриране

на

виртуалния

адрес,

основната

памет трябва

да е в

състояние да

приеме

изцяло поне

един

виртуален

сегмент,

което

означава, че

обемът на

потребителския

програмен

сегмент не

може да

надхвърля

обема на

физическата

памет.

Обикновено обемът

на

виртуалния

сегмент се

избира така,

че в

основната

памет да

могат да се

разположат

няколко

виртуални

сегмента.

Реално обаче,

поради факта,

че

програмните

сегменти

често имат

по-малка

дължина,

възможностите

допълнително

се

увеличават.

В

съвременните

операционни

системи има средства,

които

напълно

освобождават

програмиста

от грижите

свързани с

разпределението

на паметта.

Когато

едно задание

е стартирано,

това означава,

че е

определено

разположението

на програмните

му сегменти в

основната

памет и е попълнена

сегментната

таблица на

заданието.

Това по

същество

означава, че

операционната

система е

анализирала

свободните

области в

основната

памет и

знаейки

отнапред обема

Q на

програмните

сегменти на

това задание,

е определила

базовите

адреси на

физическите

сегменти в

основната

памет. Тези

адреси са по

същество

началните

адреси на

отделните

сегменти.

Тези начални

(базови)

адреси се

записват в

сегментната

таблица на

това задание,

при което се

изгражда

необходимата

връзка със

съответните

базови

адреси на виртуалните

сегменти. Освен

началните

адреси на

физическите

сегменти, в

описателя

(дескриптора)

на сегмента

се съдържат и

други

параметри,

означаващи

ниво на

привилегия,

обем на

сегмента (лимит),

разрешени

видове обръщение

(за запис, за

четене,

комбиниран и

др.), признаци

за

присъствие и

др.

По

време на

изпълнението

на

стартираната

програма от i-тото

задание се

изисква, при

всяко

обръщение

към паметта,

да се постига

еднозначно

съответствие

между

подавания от

процесора (т.е.

от

програмата)

виртуален

адрес и реалния

адрес на

търсената в

основната

памет информация.

За целта се

налага да се

извърши преобразуване

на адреса по

схема, чиято

структура

произтича от

структурата

на виртуалния

адрес.

Механизмът

на това

преобразуване

е аналогичен

на описания

при

страничната

организация

на паметта и

се реализира

чрез

таблицата на

сегментното

съответствие.

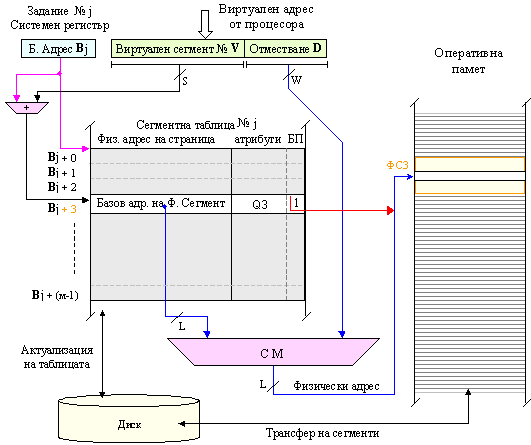

Схемата за

преобразуване

е показана на

фигура 6.4.3.1.

Фиг. 6.4.3.1. Схема

за

преобразуване

на виртуален

сегментен

адрес

Според

тази схема,

най-напред се

отчита номерът

на заданието,

чрез който в

масива (файла)

от таблици на

заданията, се

намира

сегментната

таблица на

изпълняваното

задание. Номерът

на текущо

изпълняваното

задание се

изразява от

базовия адрес

Bj на j-тата

сегментна

таблица. Този

адрес установява

съответствието

между

виртуалния

адрес на j-тото

задание и

неговото

описание, в

лицето на

таблицата на

заданията.

В j-тата

сегментна

таблица

могат да се

съхраняват

до М

на брой

описатели на

физически

сегменти на j-тото

задание.

Базовият

адрес Bj на j-тата

сегментна

таблица се

събира с

номера на

виртуалния

сегмент,

използуван

от програмиста,

в резултат на

което се

получава достъп

до

описанието

на V-тия по

ред

програмен

сегмент в

сегментната

таблица. Така

например, ако

това е

обръщение

към 785-та

клетка (D=785) в

паметта при

изпълнение

на програмен

(виртуален)

сегмент с

номер V=1 от 3-то

задание,

реалният

адрес на

клетката в

оперативната

памет се

получава

както следва:

·

В

сегментния

регистър

операционната

система

зарежда

базовия

адрес на сегментната

таблица на

задание №3,

който ще означим

В3 ;

·

След

това се

образува

сумата (

B3+V

), която

представлява

адреса на V-тия

по ред в

таблицата

описател на

физически

сегмент,

съответстващ

на заявения

виртуален сегмент.

Тъй като в

примера

виртуалният

сегмент има

номер 1 (V=1), то

получената

сума ( B3+V=B3+1

)

представлява

физически

адрес, в който

се намира

физическото

описание на

съответствието.

Както

може да се

види от

схемата,

съдържанието

на първото

поле от отворения

ред на

сегментната

таблица, се чете

като

физически

базов адрес в

основната

памет с

дължина LR. На

него се гледа

като на базов

адрес, към който

се прибавя

отместването

D.

Тъй като

базовият

сегментен

адрес е пълноразряден

следва, че

програмният

сегмент може

да започне от

произволно

място в основната

памет.

Полученият

според представената

схема реален

адрес, е

изпълнителен,

само ако

програмният

сегмент, на който

принадлежи

подавания

виртуален

адрес, се

намира в

основната

памет. За

тази цел,

всеки ред от

сегментната

таблица

съдържа

отделен разряд,

който се

нарича бит за

присъствие (БП).

Така

реалният

адрес е

изпълнителен,

ако (БП)=1.

Първоначално

съдържанието

на битовете за

присъствие в

сегментните

таблици е

нула. Когато

операционната

система

определи

къде ще

зареди

програмния

сегмент от

дадено

задание, т.е.

когато

определи

базовия сегментен

адрес, тя

прехвърля

данните от

вторичната

памет в

основната по

този адрес,

след което го

записва в

сегментната

таблица и

установява в

единично

състояние

бита за присъствие

(БП:=1).

Така че, ако (БП)=1,

обръщението

към

основната

памет се

изпълнява.

Ако

обаче (БП)=0,

това

означава, че

програмният

сегмент, към

който се

прави

обръщение, не

се намира (не

е зареден) в

оперативната

памет и

съдържанието

на

сегментната

таблица в

този ред не е

валидно. При

това положение,

обръщението

се блокира и

се генерира прекъсване.

Прекъсването

води до

предаване на

управлението

към

операционната

система,

която има за

задача да го

обслужи. По

същество, обслужващата

програма

установява в

кое задание и

в кой

програмен

сегмент е настъпила

грешката при

обръщение

към паметта.

След това

системната

програма

анализира

състоянието

на основната

памет с цел

да определи

има ли

свободна

област с

достатъчен

обем, в която

да зареди

необходимия

програмен

сегмент.

Възможно е да

се наложи

преподреждане

на вече

заредените в

паметта

програмни

сегменти

така, че

свободните

области да се

групират и

формират в

цялостна

област, достатъчна

за

поместване

на

необходимия сегмент.

Когато се

намери (или

получи) свободна

област с

достатъчен

обем, нейният

начален

адрес се

определя за

базов

сегментен

адрес. По

този адрес се

изпълнява

прехвърляне от

външната

памет на

сегмента,

след което в сегментната

таблица се

записва така

определения

базов

сегментен

адрес и се

установява

единица в

бита му за

присъствие. С

това завършва

работата на

системната

програма и управлението

се връща на

прекъснатата

потребителска

програма.

Възможно

е в основната

памет да не

се намери

достатъчно

свободно

място (дори и

след преподреждане).

В такъв случай

се налага

някой от

активните

сегменти,

намиращи се

текущо в

основната

памет, да се

дезактивира

и отново да

се повтори

процедурата

за търсене на

свободно

място.

Дезактивирането

е процес, при

който първо трябва

да се направи

избор на

сегмент за изхвърляне

от основната

памет. За

целта

процедурата

за

заместване

трябва да

реализира

определена

стратегия за

избор. След

това, използувайки

за

адресиране

сегментната

таблица,

съдържанието

на избрания

сегмент се изхвърля

във външната

памет. За

адресиране във

външната

памет

системната

програма

използува

други

таблици, в

които се

съдържа

съответствието

между

виртуалния

адрес на

съответното

задание и

неговото

място във

вторичната

памет. След

прехвърлянето

се нулира битът

за

присъствие

на сегмента в

сегментната

таблица.

Читателят

вероятно

разбира, че

проблемите,

които тук

кратко се

описват са

напълно аналогични

на описаните

в случая на

странична

организация

на

управлението

на паметта,

ето защо и

подходите за

тяхното

решаване са

общи.

Трябва

да кажем, че и

при сегментната

организация

на

виртуалното

адресно пространство

може да

възникне

ситуация на

многократно

преподреждане

и презареждане

на активни

програмни

сегменти в

оперативната

памет. Това

от своя

страна е

причина за

многократно

прередактиране

на сегментните

таблици, тъй

като се

променят

базовите

сегменти адреси.

Процесите на

неефективен

трансфер в

такива

ситуации

може

значително

да снижи

производителността

на

компютърната

система като

цяло.

В

същото време

сегментната

организация

позволява на

програмиста

да познава

съдържанието

на всеки

сегмент и

следователно

може да

въвежда свои

различни

видове защита

на паметта.

Това е

свързано с

логическото

структуриране

на заданието,

при което в

отделния

сегмент се

намира един

обект с точно

определен

тип, на който

съответствува

определен

вид защита.

Това помага

при откриване

на

програмните

грешки.

Разделянето на

заданието в

логически

несвързани

адресни

области

облекчава

съвместното

използуване

на

запомнящата

система от

няколко процеса.

Към

достойнствата

на тази

организация

може да се

отнесе

пълната

преместваемост

на програмните

сегменти,

която

позволява

автоматизиране

на процесите

на

уплътняване

в основната

памет. В

основата на

това е схемата

на

относително

адресиране.

Масивът

от сегментни

таблици може

да се съхранява

по различни

начини.

Най-често

този масив се

съхранява в

оперативната

памет. В този

случай,

преобразуването

на

виртуалния

адрес в

реален според

схемата на

сегментната

организация,

изисква две

обръщения

към паметта - едно за

извличане на

базовия

сегментен адрес

от сегментната

таблица на

заданието и

още едно за извличане

на операнда

по получения

физически

изпълнителен

адрес. Такова

реализиране

на схемата за

преобразуване

снижава

почти два

пъти

бързодействието,

ето защо се

налага

използуването

поне на един

базов

регистър за

временно

съхранение

на активния

базов сегментен

адрес.

Съществуват

практически

реализации, в

които

активната

сегментна

таблица (като

част от

масива

сегментни

таблици) се

съхранява в

регистрово

запомнящо

устройство с

произволен

или

асоциативен

достъп, имащо

високо

бързодействие.

Това

позволява

схемата за

преобразуване

на

виртуалния адрес

в реален да

бъде

реализирана

апаратно, при

което се

постига

много малко

закъснение в

процедурата

за обръщение

към оперативната

памет.

И

отново

избираме

типичните за Intel

процесори,

многократно

давани като

пример,

илюстриращи

теоретичните

постановки. В

тези

процесори

старшите 16

бита на

48-битовия виртуален

адрес, които

се наричат селектор,

съдържат 3

структурни

елемента:

< индекс; TI (Table Indicator); RPL (Requestor Privilege Level) > ,

където:

·

Индексът

отразява

номера на

заданието, т.е.

определят

съответният

му

дескриптор ;

·

Битът

TI определя

таблицата, в

която е

разположен дескрипторът,

според

правилото:

- Ако

TI=0, той се

намира в

глобалната

дескрипторна

таблица GDT;

- Ако

TI=1, той се

намира в

локалната

дескрипторна

таблица LDT.

·

Младшото

2-битово поле RPL

определя

заявеното

ниво за

привилегия,

което се

използва от

механизма за

защита.

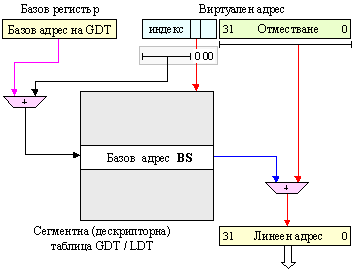

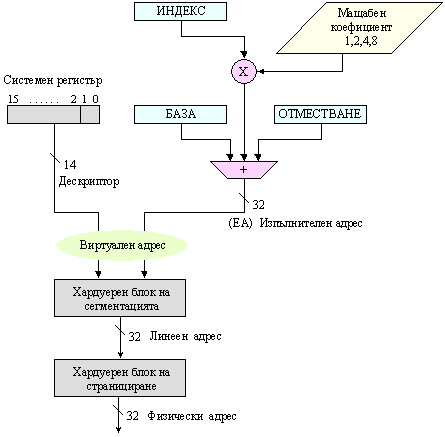

Преобразуването започва с формиране на ефективния логически адрес, според методът за адресиране, указан в машинната команда. По-нататък младшите 32 бита на виртуалния адрес се интерпретират като отместване. Отместването се събира с базовия физически адрес, който се съдържа в извлечения от сегментната таблица дескриптор. Дескрипторът представлява сложна даннова структура с дължина 8[B]. Окончателната схема на сегментната организация за управление на паметта в този процесор е представена на фигура 6.4.3.2.

Фиг. 6.4.3.2. Сегментно

преобразуване

За

избягване на

повторно

извличане на

дескрипторите,

в този

процесор се

прилага

кеширане на

дескрипторите в 64-битови

кеш-регистри

– по един за

всеки сегментен

регистър.

Някои

процесори

поддържат 3

вида

сегментни

модели, на

които тук ние

няма да се

спираме:

·

Базов

плосък модел

;

·

Защитен

плосък модел

;

·

Многосегментен

модел.

Сегментно-страничната организация

Сегментно-страничната

организация на

виртуалното

адресно

пространство

е комбиниран

вид

организация

на

управлението

на паметта.

Тя се въвежда

с цел да се

обединят

достойнствата

на двата вида

организации,

които бяха

разгледани

до момента, а

така също и с

цел да се

намали

обемът на

описателните

таблици,

така, че да се

засили

възможността

за

апаратното

им

управление.

По същество

това е

въвеждане на йерархия

в

организацията

на

управлението

на паметта от

две нива

във

виртуалното

адресно

пространство.

Прието е основното структуриране на паметта да е на страници. При това структуриране определението за сегмент се променя, като в тези условия то следва да бъде – съвкупността от определен брой страници, приели дадена програмна единица (дадено задание), представлява сегмент. Така разположението на информацията в основната памет в даден момент се описва с помощта на две таблици на съответствие – таблица на сегментите и таблица на страниците. В съответствие с казаното виртуалният адрес се структурира на три елемента, описващи принадлежността на адресируемата единица:

<№ на сегмент> <№ на страница> <Отместване> ,

т.е.

адресът

най-напред

показва в кой

сегмент S на текущо

изпълняваното

задание се

намира

търсената

клетка. Тъй

като

сегментът е

съвкупност

от страници,

вторият

елемент на

адреса

показва в коя

страница P

на сегмента S

се намира

търсената

клетка.

Окончателно

достъпът до

клетката се

конкретизира

чрез нейния

пореден

номер в указаната

страница или

още, чрез

нейното отместване

D.

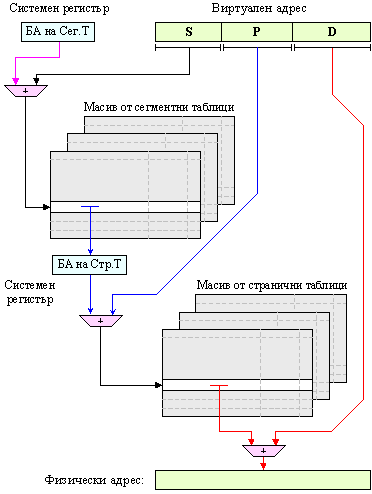

Схемата

за

преобразуване

на

виртуалния адрес

във

физически е

изобразена

на фигура 6.4.3.3,

където се

вижда, че

реалният

адрес се формира

от

отместването

и номера на

физическата

страница.

Фиг. 6.4.3.3. Схема

на смесено

преобразуване

на виртуалния

адрес

Последната

се взема от

страничната

таблица на

съответствието,

принадлежаща

на текущия

сегмент. В

тази таблица,

достъп се

получава

чрез базовия

адрес на

страничната

таблица на

текущия

сегмент и

отместването

P,

което

представлява

номера на

виртуалната

страница.

Достъпът до

страничната

таблица на

текущия

сегмент S се

осигурява

чрез

сегментната

таблица. Тя трябва

да съдържа

базовия

адрес на

страничната

таблица на

всеки

сегмент. Тези

адреси, както

и базовите

адреси на сегментните

таблици на

всяко

задание, се

определят от

операционната

система,

планираща

ресурсите на

запомнящата

система. На

схемата от

фигура 6.4.3.3 е

показан

вариант, при

който

таблиците на

съответствие

се съхраняват

в основната

памет и

достъпът в

тях е директен.

Сегментно-страничната

организация

на управлението

на паметта

позволява

лесна поддръжка

на общите

ресурси –

програми,

данни. За

целта

различни

логически

блокове от паметта

на различни

процеси се

проектират в

един и същи

блок на

физическата

памет. Този

вид

организация

обемът на

физическата

памет не

ограничава

обема на

програмата.

Възможността

програмите

да бъдат

зареждани в

оперативната

памет

частично,

това дава възможност

на системата

за

увеличаване

на пропускателната

способност,

като зарежда

и поддържа

по-голям брой

процеси.

Трансферът

на липсващи

страници

може да се

поддържа от класическия

вариант

свопинг. Този

тип комбинирана

организация

позволява

реализацията

на гъвкава

система за

защита на

софтуера от

отделните

процеси,

които

системата

поддържа.

Съществен

недостатък

на

показаната

по-горе схема

е това, че тя

изисква

масивите с таблиците

на

съответствието

да се

съхраняват в

оперативната

памет.

Съществуват

алтернативни

решения за

реализация

на схемата,

които се

основават на

асоциативния

метод за достъп

в таблиците.

Реализацията

се постига с

помощта на

асоциативните

TLB и TSB буфери,

чиято

структура и

функциониране

изяснихме

подробно в

предидущия

пункт.

Сегментно-страничната

организация

на управлението

на паметта се

практикува

във всички

съвременни

процесорни

архитектури.

При това

трите вида

организация

могат да

бъдат

избирани поотделно.

С цел

читателят да

добие

представа за

сложността

на

цялостната

схема, по

която се получава

действителният

адрес, с

който се

достига

оперативната

памет, като

се излезе от

съдържащото

се в

машинната

команда отместване

и се мине

през всички

схеми за преобразуване,

по-долу на

фигура 6.4.3.4 е

представена

една

обобщена

схема за

формиране на

адреса в

събирателната

архитектура iA-32.

Фиг.

6.4.3.4. Формиране

на

физическия

адрес в

архитектурата

iA-32

Изпълнителният

адрес (ЕА – effective address) се

получава в

архитектурата

iA-32 според

указаните в

командата

отместване, мащабен

коефициент и

съдържания на

индексен и

базов

регистри,

според

избраната от

командата

формула на

съответния

метод за

адресиране.

Старшите

14 бита на

съответно

указания в

командата

сегментен

регистър

(един от 6-те: CS, SS, DS, ES, FS, GS) определят

конкретния

дескриптор,

който използван

като индекс в

таблицата на

сегментните

дескриптори,

позволява да

бъде извлечен

32-битовият

базов адрес.

Последният

се събира с

изпълнителния

адрес и се

получава 32-битовият

линеен адрес.

Блокът за

странициране

преобразува

този адрес

във 32-битов

физически

адрес.

За

допълнителни

реални

практически подробности

препоръчваме

на читателя

следния

адрес:

https://en.wikipedia.org/wiki/Physical_Address_Extension -

Page_table_structures .

Следващият

раздел е:

6.4.4.

Особености

на командния

цикъл в условията

на виртуална

памет