Последната

актуализация

на този

раздел е от 2019

година.

3.1

ТРИГЕРИ – Latch, Master-Slave, Edge

логически

структури и

функциониране

Запомнящите

градивни

елементи, т.е.

тригерите,

имат

изключителна

роля в

проектирането

на

логическите

схеми и

затова тук ще

бъдат

разгледани

отделно. В

теорията на

крайните

автомати те

се определят

като

елементарни

крайни

автомати и

като такива

се описват

чрез времеви

логически

функции, въз

основа на

концепцията

за дискретното

време.

Разглеждането,

което ще

направим тук,

няма да се

отнася до

тяхната

теория, а до

възможностите

им и от

необходимостта

в дадено

време и в

дадено място,

да

реализират

своето

предназначение

според

съответния

алгоритъм в

проектираната

логическа

структура.

Още

тук искаме да

подчертаем,

че основното

предназначение

на тригерите

е да

записват и да помнят

дълготрайно

във времето

дадена

логическа

стойност.

Ето защо

читателят не

следва да

употребява в

логическите

схеми тригери,

ако не му е

необходимо

да помни във

времето

дадена

логическа

стойност.

Начинът на

превключване

на

запомнящия

елемент няма

нищо общо с

предназначението

му, но е определящ

за избора му.

Превключването

на тригерите

пък се

определя от

вътрешната

им логическа

структура.

Така

същественият

извод тук е,

че изборът на

най-подходящия

тригер се

определя от перфектното

разбиране на

същността на

микрооперация

запис, т.е. на

нейните

изисквания и

на начина на

нейното

изпълнение.

При

проектиране

на логическите

структури

проектантът

следва също

добре да

разбира:

· Какво

е

поведението

на данните и

кога (в кой

момент) една

или много

логически

стойности се

налага да

бъдат

запомнени

(съхранени) и

защо

всъщност се

налага това;

· Какъв

метод за

запис следва

да се

приложи, както

на всяка една

отделна

логическа

стойност,

така и цялата

съвкупност

от такива в даден

момент;

· Какъв

запомнящ

елемент е

най-подходящ

за целта (с

каква

структура и с

какво

управление);

· Какви

манипулации

(микрооперации)

на състоянието

на

запомнящите

елементи още

ще се налага

да бъдат

изпълнявани

във времето

(разбирайте

по време на

изпълнение

на

алгоритъма,

по който

функционира

логическата

структура

като цяло).

Всяка

манипулация е

по същество

запис (по

един или друг

начин) на

нова

логическа стойност

в запомнящия

елемент.

Нулирането на

състоянието

на тригера,

например, е

всъщност

запис на

логическа

нула;

· Всяка

манипулация

на

съдържанието

на запомнящия

елемент се

постига чрез

някакъв кратковременен

логически

импулс,

наричан управляващ

сигнал.

Тригерите

са такива

логически

схеми, които

имат два

изхода (прав

и инверсен).

Входовете им

могат да бъдат

синтезирани

в различни

комбинации и

с различни

функции –

такива,

каквито са

необходими

на

проектанта.

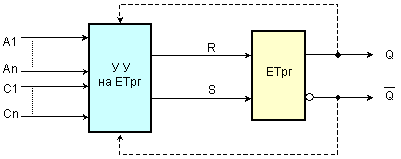

Общата

логическа

структура,

към която

може да бъде

подведена

всяка

тригерна

схема, е

представена

на фигура 3.1.1

Фиг.

3.1.1. Обща

логическа

структура на

тригер

Както

може да се

види, тя се

състои от два

елемента – ЕТрг

(елементарна

тригерна

схема тип RS) и устройство

за

управление

на

елементарния

тригер – УУ на ЕТрг.

Към

управляващото

устройство

са подведени

множество

външни

информационни

сигнали {A1÷An};

множество

тактови (или

още

управляващи)

сигнали {C1÷Cn}, а така

също и

възможните

вътрешни

обратни

връзки от

изходите на

тригера,

показани на

фигурата с

пунктирни

линии. Според

тази схема

всички

възможни

тригерни

схеми съответстват

в пълна

степен на

теорията на

крайните

автомати.

Всички

тригерни

схеми, които

ще бъдат

споменати

по-нататък

тук, работят

в потенциална

система на

сигналите.

Изменяйки

организацията

в

устройството

за

управление

на

елементарния

тригер и подключването

на обратните

връзки (виж

фигура 3.1.1)

могат да

бъдат

получени

различни по

функциониране

тригерни

схеми. Така

например,

тригерна

схема с един

информационен

вход А1, който може

да подаде две

логически

стойности (0 и 1) и

пет

логически

състояния на

изхода си: 0, 1, Q, not(Q)

и X, може да

бъде

синтезирана

така, че да се

получат до 25 (52=25)

различни по

функциониране

варианта. Много

от тях са

практически

безсмислени,

а други са

еквивалентни

помежду си.

Изходните състояния,

които бяха

посочени

следва да се разбират

по следният

начин:

·

Състояние

0 –

тригерът се

намира в това

състояние (Q=0)

постоянно

във времето,

независимо

от логическата

стойност на

входа А1;

·

Състояние

1 –

тригерът се

намира в това

състояние (Q=1)

постоянно

във времето,

независимо

от логическата

стойност на

входа А1;

·

Състояние

Q –

състоянието

на тригера не

се изменя при

изменение на

логическата

стойност на

входа А1, т.е.

тригерът

помни

старата

стойност и за

да се

превключи е

необходим

допълнителен

управляващ

сигнал;

·

Състояние

not(Q) -

състоянието

на тригера се

променя на

противоположното

при

изменение на

логическата

стойност на

входа А1;

·

Неопределено

състояние Х – това

състояние на

тригера се

характеризира

с това, че в

процеса на

действие на

входния

информационен

сигнал,

изходните

логически

нива в двете

рамена на

тригера Q и not(Q)

са еднакви (Q=not(Q)=1

или Q=not(Q)=0), а след

изчезване на

входния

сигнал А1

тригерната

схема се

превключва

лавинообразно,

при което не

може да се

гарантира

какво ще бъде

крайното устойчиво

състояние на

тригера – то може

да бъде както

Q=0, така и not(Q)=1.

Крайното

състояние е

функция от

параметрите

на

електронните

елементи на

реалната

схема в двете

рамена на

тригера.

Забележка: В

горните

обяснения наличие

или поява

на

информационния

сигнал А1

следва да се

разбира като поява

на логическа единица,

т.е. А1:=1. Изчезване,

отнемане

или завършване

на

действието

на

информационния

сигнал следва

да се разбира

като поява

на логическа

нула – А1:=0.

Запознаването

със

запомнящите

елементи, изучаването

им в оня

смисъл, който

пояснихме в

началото,

следва да се

извърши в подходящ

ред, ето защо

за тази цел

тук се нуждаем

от

най-подходящата

им

класификация.

Различават

се три вида

класификации

на запомнящите

елементи:

1. Класификация

според

метода за

управление.

Методите

за управление

(разбирайте

управление

на превключванията)

са два и

тяхната

същност е

изложена в книга [1]. Според

методите за

управление

на записа на

нова

логическа

стойност,

тригерите са асинхронни

и синхронни.

Асинхронните

тригери се

разделят на

два типа:

·

Тригери,

които се

превключват

от нивото на

информационния

сигнал;

·

Тригери

с вътрешно

закъснение.

Изменение

на

състоянието

на

асинхронните

тригери се

извършва в

резултат на

изменение

(превключване)

на

логическите

стойности,

подавани на

информационните

им входове. С

други думи,

всяка

активна

комбинация,

подавана на

информационните

входове, е

причина за

превключване

на тригера.

От това разбиране

следва, че

тригерът

помни

записаната

логическа

стойност до

момента на

следващата

активна

комбинация.

В такива

тригери актът

на запис не

се заповядва

отделно или

специално.

Синхронните

тригери се

разделят

също на два

типа:

·

Тригери,

които се

превключват

от нивото на управляващия

сигнал

(превключването

се извършва с

постъпването

на

управляващия

сигнал). Тези

тригери

могат да бъдат

еднотактни и

многотактни;

·

Тригери

с вътрешно

закъснение

(превключването

се извършва

след

изчезване на

управляващия

сигнал). Тези

тригери по

правило са еднотактни.

Изменението

на

състоянието

на синхронните

тригери се

постига с

помощта на

нарочно предназначени

за целта

сигнали

(управляващи

сигнали),

които се

подават на

специални

входове.

Специалните

входове са

два вида: входове

за

принудително

установяване

на тригера и входове

за

управление

на записа на

новата

логическа

стойност,

постъпваща по

информационните

входове на

тригера. За

да се избегне

възможния

конфликт от

едновременно

подаване на

управляващи

сигнали и по

двата вида

специални

входове

(например, за

установяване

в нулево

състояние и

едновременно

с това

записване на

нова

логическа

стойност) е

желателно

логическата

структура на

тригера да е

така

синтезирана,

че приоритетни

да се явяват

функциите на

специалните

входове за

принудително

установяване.

В синхронните

тригери

актът на

запис се

заповядва,

т.е. той се

изпълнява в

онзи момент,

който се

определя по

съответен

начин от

управляващите

сигнали и

неговата

вътрешна

логическа

структура.

Следва добре

да се

разбира, че

установяването

на дадена

тригерна

схема в определено

логическо

състояние

при наличие на

разнообразни

входни

сигнали може

да бъде

постигнато

по различни

начини. Това

води до

необходимостта

да бъде

извършван

избор на

най-оптималния

вариант.

2. Класификация

според вида

на

информационните

входове.

Чисто

теоретично,

при n-входова

тригерна схема

от вида,

показан на

фигура 3.1.1,

могат да бъдат

създадени 5(2n) на брой

тригерни

схеми от

различен тип.

Но в реалното

логическо

проектиране,

приложение

са намерили

сравнително

не голям брой

типове

тригерни

схеми, към

които преди

всичко се

отнасят

следните: RS, D, DV, JK, T, TV,

E, R, S. Така упоменатите

наименования

реализират

различаването

на отделните

тригери

според

функционалността

на

информационните

(данновите) им

входове.

Изказването

“RS-тригер”

означава, че

става дума за

тригер, който

има два даннови

входа –

съответно

R-вход (reset) и

S-вход (set)

Специална

електронна

схема носи

наименованието

тригер на

Шмит.

Общо

приетото

означение на

входовете,

според

тяхното

функционално

предназначение,

е следното:

S (Set

–

установяване).

Прав вход за

установяване

на тригера в

състояние 1;

PR (Preset

–

установяване

предварително).

Вход за установяване

на тригера в

състояние 1;

R (Reset

–

възстановяване).

Прав вход за

установяване

на тригера в

състояние 0;

CL (Clear

– изчистване

предварително).

Вход за

установяване

на тригера в

състояние 0;

J (Jerk

– внезапно

включване).

Прав вход за

установяване

на тригера в

състояние 1;

K (Kill

– внезапно

изключване).

Прав вход за

установяване

на тригера в

състояние 0;

T (Toggle

–

превключвател).

Прав вход за

превключване

на тригера в

противоположно

състояние;

D (Delay

– задържане).

Вход за

превключване

на тригера в

същото

състояние;

C (Clock

–

синхронизация).

Прав вход за

управление на

записа в

тригера.

V (Valve

– клапан). Прав

вход за

разрешение

на функцията

запис.

Елементарният

тригер (виж

фигура 3.1.1) е от

тип RS и се характеризира

с това, че

входната

информационна

комбинация R=1, S=1

за тригерите

с право управление

(или R=0, S=0 за

тригерите с

инверсно

управление) е

забранена,

тъй като тя

изисква

едновременно

превключване

в състояние 1

и в състояние

0. Както беше

пояснено

по-горе, при

такива

входни

комбинации,

състоянието

на тригера се

приема за

неопределено

– Х, т.е. двата му

изхода са в

една и съща

логическа

стойност.

Неопределеността

в

състоянието

идва с

изчезване на

забранената

комбинация,

когато в

резултат на

лавинообразните

електронни

преходни процеси,

крайното

състояние на

тригерната

схема е непредсказуемо.

Алтернативата

на този

тригер е

тригер JK, който

се

превключва

логично

(според

своята таблица

на истинност)

при всички

възможни

входни

комбинации.

Общото за

тези два

тригера е, че

те имат по

два информационни

входа, което

дава

възможност за

реализация

на различни

схеми за

запис на информация

в тях.

Основните

схеми за

запис на нова

логическа

стойност в

един тригер са

две и се

наричат еднофазна

и парафазна.

Тези

наименования

на схемите за

запис са дадени

във връзка с

това дали

записваната

логическа

стойност се

довежда

(разпространява)

до тригера

само с едната

си фаза (например

правата) или

и с двете

едновременно

(и правата и

инверсната).

Разпространението

или

довеждането

на дадена

логическа

стойност от

една точка до

друга точка

се реализира

чрез

логическа

връзка. На

практика

логическата

връзка

представлява

някакъв вид проводник

(електрически

или

оптически).

Тригер

от тип D има

само един

информационен

вход. Постъпващата

по този вход

логическа

стойност се

записва и

съхранява в

тригера.

Единствено

тригерът от

тип Т е

по-богат във функционално

отношение.

Според

логиката на

превключване

на този

тригер,

входната стойност

влиза във

функционална

връзка със

съдържащата

се (със

запомнената)

в тригера

стойност и те

заедно

формират

новата

стойност,

която тригерът

ще помни в

следващите

моменти. Функцията

на това

превключване

се нарича неравнозначност

или още сума

по модул 2. По

тази причина

този тригер е

единственият,

с който се

реализират

броячи и

натрупващи

суматори.

Подобни

свойства има

и JK-тригерът.

3. Класификация

според

вътрешната

логическа

структура.

Тази

класификация

е най-съществената,

тъй като тя

определя

функционирането

на тригерите

и

възможностите

за тяхното използуване

при

реализиране

на микрооперациите,

с които е

натоварен

логическият

възел, в

състава на

който те са

включени.

Според

вътрешната

си логическа

структура

тригерите се

класифицират

от тип:

·

Latch

- (ключ, в

смисъла на

запомнящ, т.е.

паметлив).

Тригер от

този тип се

определя

като

еднотактен,

едноетажен

тригер,

превключващ

се при смяна

в нивото на

информационните

сигнали. По

тази причина

го наричат

още тригер-памет

или просто памет.

·

Master-slave - (господар и слуга).

Тригер от

този тип се

определя

като двутактен,

двуетажен

тригер,

превключващ се

по ниво.

Когато тази

структура е

синхронна,

моментът на

запис

(фиксиране)

на информационните

сигнали се

определя от

появата или

от

изчезването

на

управляващия

сигнал за

запис, т.е. от

неговия

преден или

заден фронт.

Неговият

логически

синтез цели

да защити

схемата от

вътрешни

състезания,

когато тя е

обхваната от

обратни

връзки. По

тази причина

се нарича още

противосъстезателен

тригер.

·

Edge -

(фронт).

Тригер от

този тип се

определя

като

двутактен,

двуетажен

тригер,

превключващ

се по

съответния

фронт на управляващия

сигнал.

Механизмът

на това превключване

обаче е

различен от

този в предидущата

структура.

Ето защо

тригерите с

тази

структура се

наричат още с

динамично

управление

или тригери-закопчалки,

или още самоблокиращи

се тригери.

Динамичното

управление

на тригера,

т.е. на записа,

се реализира

от специална

асинхронна

логическа

схема,

известна

като схема на

Хуфман (David A.

Huffman).

Изменението

в нивото на

информационните

сигнали е без

значение за

състоянието

на тези

тригери във

всички

моменти,

освен в момента,

определен от

фронта на

управляващия

сигнал за

запис. Това

са тригери,

които се приемат

за

най-надеждните

по отношение

на записа на

данни в тях.

Както

вече беше пояснено,

първичната

тригерна

структура е тази

на

RS-тригерите.

Когато тя е

построена чрез

логически

елементи от

тип ИЛИ-НЕ,

тригерът се

нарича с

право

управление,

защото

активната

стойност на

информационните

сигнали,

причиняваща

превключването

му, е единицата.

Затова се

говори още,

че такъв

тригер се превключва

по единиците.

Когато

структурата

е построена

чрез

логически

елементи от

тип И-НЕ,

тригерът се

нарича с

инверсно

управление,

защото

активната

стойност на

информационните

сигнали,

причиняваща

превключването

му, е нулата.

Затова се

говори още,

че такъв

тригер се

превключва

по нулите.

Тяхното

функциониране

зависи от

типа на

градивните

логически

елементи и

логическата

структура

която

реализират,

ето защо е

особено

полезно

последната

да се познава

добре.

Тригери

със

структура Latch

Първичните

RS структури

се определят

още като

еднотактни,

едноетажни,

асинхронни,

от тип Latch

и работещи по

ниво. Всяко

едно от тези

определения

има своята

същност и се

употребява в

съответните

обяснения

като

най-подходящото.

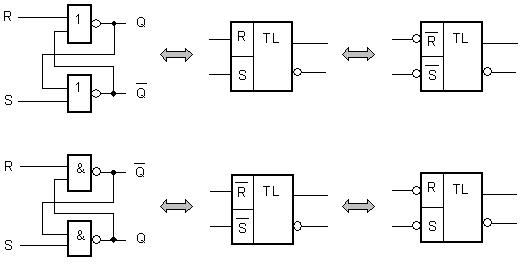

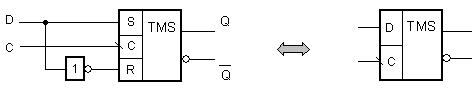

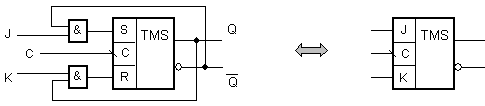

Логическата

структура на

тези тригери

и техните

условни

графични

означения са

показани на

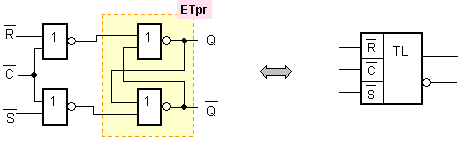

фигура 3.1.2.

Фиг.

3.1.2. Логическа

структура и

условно

графично означение

на

първичните Latch

тригери

Тук

ние няма да

се

занимаваме с

теоретичния

синтез на

тези

логически

схеми, които

се определят

като

елементарни

автомати или

като

елементарни

тригери. Само

ще припомним,

че тяхното

основно

свойство не е

гарантирано

при подаване

на така наречените

“забранени”

входни

комбинации.

За тригера с

право

управление

забранена е

комбинацията (R=1,S=1),

а за тригера

с инверсно

управление –

комбинацията

(R=0,S=0).

Записът

на

информация в

представените

на фигура 3.1.2

тригери, е

възможен по

два начина – еднофазно

или парафазно.

И в двата

случая обаче

записът се

определя

като асинхронен.

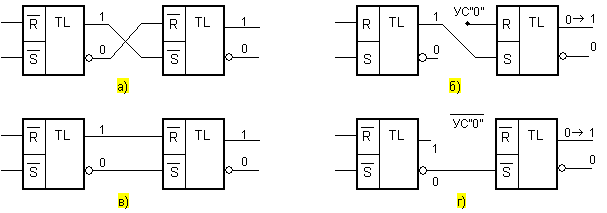

Логическите

връзки, които

осъществяват

записа

![]()

са

илюстрирани

на фигура 3.1.3,

където

рисунка а)

показва

асинхронен

парафазен

запис в десния

тригер на

съхраняваната

в левия тригер

логическа 1. И

двата

тригера в

рисунка а) са

с право управление.

На

рисунка б) от

фигура 3.1.3 е

показано

свързването

на приемащия

(десния)

тригер,

когато той

реализира

еднофазен

запис на

логическата

стойност,

подавана от

левия тригер.

За да се

запише

правилната

стойност,

приемащият

тригер се

нулира

предварително

с помощта на

допълнителен

управляващ

сигнал УС”0”,

чиято

активна

стойност е 1

![]()

Добре

е

проектантът

да разбира,

че ако кръстоса

изобразените

на фигура 3.1.3

връзки между

предаващия и

приемащия

тригери, ще

реализира

едновременно

със записа и

в допълнение

операция

логическа

инверсия на

записваната

логическа

стойност, т.е.

микрооперацията

ще бъде

![]()

Поради

асинхронното

свързване на

тези тригери,

тяхното

функциониране

в двете схеми

(рисунки а,в) и

(рисунки б,г)

от фигура 3.1.3, е

различно.

Приемащият

тригер от

рисунка а)

например, не

може да изяви

свойството

си

паметливост,

тъй като се е

превърнал в повторител

на

състоянието

на подаващия

тригер. В

рисунка б)

свойството

паметливост

в приемащия

тригер се

изявява в пълна

степен. След

нулирането

му той остава

в състояние

нула, ако

състоянието

на предаващия

тригер е също

нула. Когато

обаче левият

тригер се

превключи в

единица,

същата ще се

запише в

приемащия

(десния)

тригер. Ако след

този запис

левият

тригер

загуби своята

единица (ако

се превключи

в състояние

нула),

десният

тригер ще

продължава

да съхранява

запомнената

преди това

единица до

момента,

когато не

бъде

повторно

нулиран с помощта

на

управляващия

сигнал УС"0".

Подобно

е

поведението

и на

тригерите с

инверсно управление,

чието

еднофазно и

парафазно

свързване е

показано на

фигура 3.1.3,

рисунки в) и г).

Необходимо е

да се обърне

внимание на

факта, че

активната

стойност на

нулиращия

сигнал в този

случай е 0.

Фиг.

3.1.3. Еднофазен

и парафазен

запис на

информация в

първични

тригери

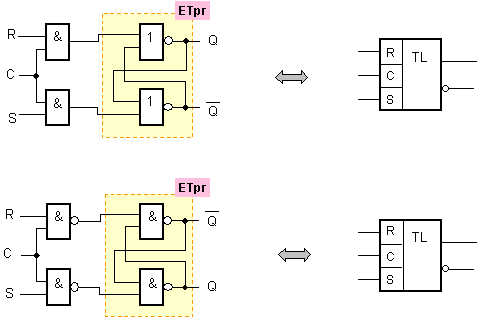

Споменатите

по-горе

тригери се

превръщат в синхронни,

когато им се

добави

специален

вход за управление

акта на

запис, както

е показано на

фигура 3.1.4.

Фиг.

3.1.4. Реализация

на синхронен

вход в

първичните Latch

тригери

Както

уважаемият

читател вече

забелязва, УГО

на тригерите

от фигура 3.1.4 са

напълно еднакви,

но те

съответстват

на различни

вътрешни

структури,

което е много

показателно и

следва да се

има предвид

при

изучаването и

употребяването

на реалните

логически елементи.

Докато

сигналът С в

схемите от

фигура 3.1.4 има

стойност 1 (а

това може да

продължи

неограничено

дълго време), входните

информационни

сигнали

могат да превключат

тригера

многократно,

тъй като той

по това време

работи в

асинхронен

режим. Актът

на запис

(или още

фиксация) в

тези схеми се

осъществява

в момента на

задния фронт

на сигнала С, т.е.

в момента,

когато се

затварят

входните даннови

линии на

тригера, ето

защо, ако

искаме

записът да

бъде

надежден, то точно в

този момент

следва да

осигурим стабилност

на

логическите

стойности,

подавани на

информационните

входове. От

този момент

нататък

схемата

проявява свойството

си

паметливост,

тъй като,

когато управляващият

сигнал

изчезне, т.е.

стане нула,

информационните

входове на

тригера се

препречват

от затворилите

се входни

схеми И,

които често,

поради тази

си функция,

се наричат

още врати. Казаното

е

илюстрирано

на

следващата

времедиаграма,

която

изобразява

превключвания

в схемата от

фигура 3.1.4.

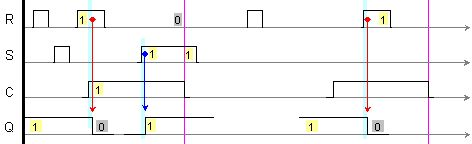

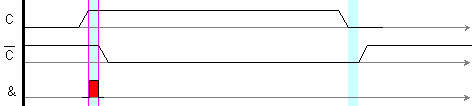

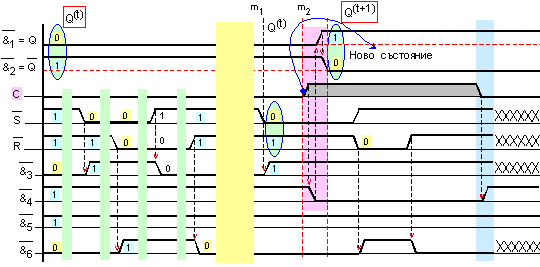

Фиг.

3.1.4-а. Синхронен

запис на

данни в

първични Latch RS-тригери

На

времедиаграмата

се вижда, че

завареното

състояние на

тригера

(фигура 3.1.4) е

единица (Q=1). С

течение на

времето, в

отсъствие на

сигнал С, се

появява

единица на

вход R, а

след нея

единица на

вход S, които обаче не променят

състоянието

на тригера, тъй като

неговите

входове са

затворени (С=0). Промяната

става

възможна с

появата на

сигнал С (С=1).

Тъй като по

това време на

вход R има единица,

тригерът се

превключва в

състояние

нула (Q=0). Синята

ивица

изобразява

закъснението

на изходната

логическа

стойност,

което се дължи

на

латентността

на

логическите

елементи. С

течение на

времето,

докато

входовете на

тригера са

все още

отворени (С=1)

се появява

единица на

вход S,

което

предизвиква

повторно

превключване

на тригера (Q=1). В

момента на

изчезване на

сигнала С не

се наблюдават

изменения на

входните

стойности, в

резултат на

което

тригерът

остава в състояние

единица.

Появилият се

след това импулс

на вход R

не е в

състояние да

превключи

тригера, тъй като

неговите

входове по

това време са

затворени (С=0).

След

повторната

поява на

сигнал С,

изобразената

единица на

вход R

успява да

превключи

тригера в

състояние нула

(Q=0), след

което няма

условия за

други

превключвания.

Логическата

реализация

на тригерните

схеми по

теория е

много

разнообразна,

но само малка

част от това

разнообразие

се предлага

на пазара. С

дълбоко

разбиране и чувство

на

отговорност

желаем да

внушим на читателя

това положение,

за да го

предпазим от

копиране на

готови

решения,

които в

конкретните

ситуации не винаги

биха се

оказали

най-подходящите.

Бихме желали

да

подчертаем,

че само

творческият

подход в

проектирането

би го довел

до онези

решения,

които

вероятно е

търсил и които

са му били

необходими.

Никой не е

казал, че

следва да се

използуват

само тези

тригерни

структури,

които се

предлагат на

пазара. Желаните

функции на

даден тригер

могат да бъдат

постигнати

само след

конкретен

логически

синтез.

Ще

илюстрираме

казаното с фигура

3.1.5, където е

показано

въвеждане на

синхронен

вход в

RS-тригер с

право

управление при

използуване

на еднакви

градивни

елементи

ИЛИ-НЕ.

Резултатът,

който се

получава, е

RS-тригер с

инверсно

управление,

който се синхронизира

по

инверсните

стойности на

сигнала С –

нещо твърде

различно от

показаното

на фигура 3.1.4.

Фиг.

3.1.5. Реализация

на синхронен

вход с

еднакви елементи

в Latch тригер

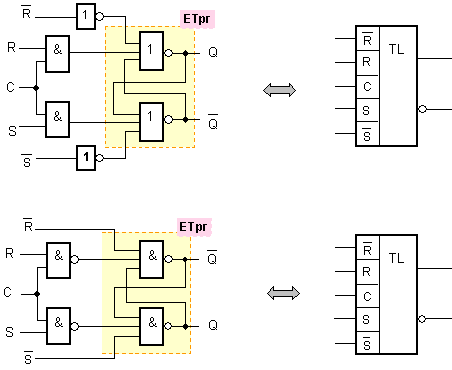

На

фигура 3.1.6 са

представени

логически

схеми на

RS-тригери,

допълнени с приоритетни

установъчни

входове. За

нормална

работа на

тригерните

схеми на тези

входове

трябва да

бъдат

осигурени във

времето

неактивни

логически

стойности. Отново

се вижда, че

УГО на тези

елементи са еднакви,

но техните

вътрешни

схеми – не.

Фиг.

3.1.6. Реализация

на

установъчни

входoве в

първичните Latch

тригери

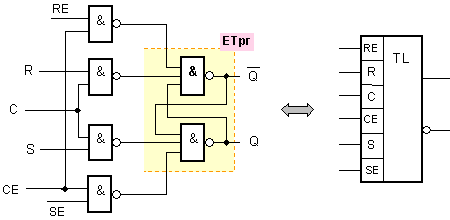

Ако

Проектантът

желае, може

да въведе

допълнителен

управляващ

сигнал СЕ,

който да бъде

разрешаващ

за функциите

на приоритетните

установъчни

входове. Тази

възможност е

показана на

фигура 3.1.7, в

логическата

схема на

синхронния

тригер от

фигура 3.1.6,

изграден

чрез схеми

И-НЕ.

Фиг.

3.1.7. Реализация

на

разрешаващ

сигнал към

установъчните

входoве в Latch

тригер

Ако

внимателно

обаче се

анализира получената

схема ще се

забележи, че

синхронната

двойка

входове C(R-S) е

подключена

към елементарния

тригер така,

както е

подключена и

синхронната

двойка

входове CE(RE-SE), т.е.

двете двойки

са

еквивалентни.

В резултат на

това получената

схема може да

се интерпретира

като тригер,

към който има

изградени

два

еквивалентни

синхронни

входа за връзка

с два

различни

източника на

информация.

Записът

на

информация в

тригери от

тип RS трябва

да бъде

съобразен с

факта, че те

имат два

информационни

входа,

независимо

дали са

синхронни

или

асинхронни.

Свързването

на логически

възли,

например

паралелни регистри,

изградени от

такива

тригери, в този

случай

изисква по

два

проводника

за всяка

логическа

стойност, за

всеки разряд,

които да

пренасят

едновременно

и правата и

инверсната й

фаза. Това не

винаги е

добър

вариант,

особено във

вътрешността

на

интегралните

схеми, където

проточването

по два проводника

за пренасяне

на един бит

информация е особено

неефективно

решение. Ето

защо масово

се прилагат

тригерни

схеми с един

информационен

вход.

Такива схеми

се получават

много лесно

на базата на

първичен

тригер, на

входа на

който се

възстановява

липсващата

фаза на подаваната

логическа

стойност.

Такива

тригерни

схеми се

наричат от

тип D,

или просто

D-тригери (Delay –

задържане).

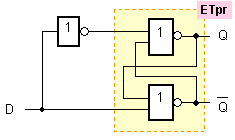

Елементарната

асинхронна

D-тригерна

схема е показана

на фигура 3.1.8.

Анализът на

тази схема

показва, че

изходът Q

повтаря във

всеки момент

логическата

стойност на

входа D. Това

определя

схемата като повторител,

чието

практическо

изпълнение

внася известно

закъснение в

изходното

превключване

по отношение

на входното. Такава

схема не

притежава

свойството

паметливост,

ето защо

асинхронни

D-тригери не се

използват – те са

безсмислени.

Фиг.

3.1.8. Първична

асинхронна

D-тригерна

схема (повторител)

За да

се прояви

свойството

паметливост

, (същност на

елементарния

тригер ЕТрг)

в схемата от

фигура 3.1.8

трябва да се

въведе управляващ

сигнал за

управление

акта на запис

на новата

входна

логическа

стойност. Така

се получават

синхронните

тригерни

схеми от тип D,

чието

изпълнение

върху

елементарни

RS-тригери с

право

управление е

показано на

фигура 3.1.9.

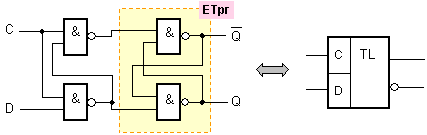

Фиг.

3.1.9. Синхронни

едноетажни Latch

D-тригери

Синхронен

D-тригер с

инверсно

управление е показан

на

следващата

фигура 3.1.10

Фиг.

3.1.10. Синхронни

едноетажни Latch

D-тригери

Всичко

казано

по-горе за

превключването

на

синхронните RS-тригери,

се отнася и

за току що

представените

синхронни D-тригери –

записът

(фиксацията)

на нова логическа

стойност се

осъществява

в момента на

отпадане на

синхронния

сигнал С.

Говори се, че

такива

тригери се

управляват

по ниво.

Тук

обаче още

веднъж

искаме да

предупредим

читателя за ненадеждността

на някои

логически

схеми на Latch D-тригери,

които различни

автори

предлагат в

своите

публикации. Без

да цитираме,

ще

представим

една много често

предлагана

логическа

схема (фигура

3.1.10-а).

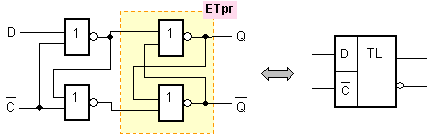

Фиг.

3.1.10-а. Синхронен

Latch

D-тригер с

пулс-генератор

Идеята,

която се

предлага

чрез горната

схема се

състои в

използването

на пулс-генератор

на кратък

единичен

импулс, който

бързо (за

много кратко

време) да

отвори входа

на D-тригера,

с надеждата

последният

да успее да

се превключи

и да фиксира

входната

логическа

стойност D. Очаква се,

краткото

действие на

синхронния

импулс да е достатъчно

кратко, така

че входната

стойност D да не

продължава

да

въздейства

на RS-тригера (ЕТрг)

след

неговото

превключване. Дали

изказаните

очаквания

могат да се

сбъднат, ще

поясним

по-долу. Сега,

на следващата

времедиаграма,

ще поясним

същността на

пулс-генератора.

Фиг.

3.1.10-б. Функциониране

на

пулс-генератор (импулс

при преден

фронт)

При

силно

удължените

фронтове на

превключващите

се сигнали е

изобразен

съвършено идеалния

единичен

импулс

формиран от

конюнкцията

(СÇnot(C)), което

е направено

умишлено.

Теоретично

тази

конюнкция е

константа

нула (0), но в

резултат на

закъснението

на новата

логическа стойност

С на изхода

на инвертора not(C), се

очаква

схемата “И” да

успее да

фиксира времевия

интервала на

двете

единици в сигналите

С и not(C). Това се

случва само

при поява на

преден фронт

в сигнала С,

който по идея

заповядва

запис на

входната

стойност в

тригера.

Логическата

схема на

пулс-генератора

е известна

още под

наименованието

“фронт-детектор”.

Най-различни

логически

схеми, които

са

синтезирани

при

използването

на реалните

закъснения в

логическите

елементи,

читателят

може да

разгледа на

този сайт в глава 5 на

книга [5].

А сега

ще изложим

нашите

аргументи против

този начин на

управление

на

представения

на фигура 3.1.10-а

синхронен D-тригер.

Генерираният

единичен

импулс е с продължителност

t

секунди. Това

време не е

достатъчно

за превключване

на всички

елементи в

схемата на тригера.

За

превключване

и трайно

установяване

на новото

състояние на

тригера са

необходими

минимум 3.t

секунди. За

да се

осигурят

условията,

при които

записът на

нова

логическа

стойност в тригера

е възможна,

трябва да се

увеличи продължителността

на единичния

управляващ

импулс. За

целта трябва

да се добавят

още няколко

последователно

свързани

инвертора в

схемата на

пулс-генератора.

Това ще усложни

и оскъпи

схемата на

тригера и тя

отново ще

бъде

ненадеждна.

Дали

продължителността

на единичния

импулс ще е

достатъчна

или не, това

схемата не

гарантира.

Нейните

параметри се

влияят още и

от

температурата

на експлоатация.

Освен това

използването

на пулс-генератора

обвързва в

пряка

зависимост

продължителността

на

генерирания

импулс с продължителността

на сигнала С.

И ако за един

тригер

записът може

да бъде

успешен, то

за съседния в

един

регистър,

това не е

гарантирано,

тъй като

производствената

технология не

гарантира

еднаквост на

техническите

параметри на

отделните

логически

елементи.

Съществуват

и други ненадеждни

тригерни

схеми, които

ще

коментираме

по-нататък в

хода на изложението.

Тригерите

със

структура Latch

са много

полезни и се

предпочитат

винаги, когато

е възможно,

защото са

икономични и

евтини. Ще

представим

още някои

допълнения, които

допълват

възможностите

им и им придават

гъвкавост.

Ако се

повтори

подходът, който

беше

илюстриран

чрез фигура 3.1.7

и към схемите

от фигура 3.1.9 и

фигура 3.1.10 се

добави още

един управляващ

вход, за да

играе ролята

на разрешение

за

превключването

на тригера,

то ще се

получи

тригерна

схема от тип DV (Data Valid). Един от

вариантите на

такава схема,

построена

чрез

логически елементи

И-НЕ, е

показан на

фигура 3.1.11.

Фиг.

3.1.11. Синхронен

едноетажен Latch DV-тригер

Записът

на

информация в

синхронния

DV-тригер

зависи от

подаваната

на вход V

логическа

стойност.

Ясно се

вижда, че

тригерът

функционира

само когато V=1.

На

следващата

фигура 3.1.12 са

представени

примерни

логически

схеми на

S-тригер и на

R-тригер с

право

управление,

построени с

логически

елементи

И-НЕ.

Фиг.

3.1.12. Синхронен

едноетажен Latch S-тригер

и R-тригер

Показаните

синхронни S и R

тригери

представляват

тригери с два

информационни

входа. Когато

конюнкцията

им има

стойност

единица (RÇS=1),

S-тригерът се

превключва в

единично

състояние, а

R-тригерът – в

нулево

състояние.

Избрания

даннов вход (S или R)

става

доминантен,

което

променя

възможността

на

“забранената”

входна

комбинация (R=1, S=1).

Обединяване

на описаните

две

възможности

довеждат до

логическата

схема на

Е-тригер,

който е

показан на

фигура 3.1.13.

Фиг.

3.1.13. Синхронен

едноетажен Latch

Е-тригер

Е-тригерът

не променя

своето

състояние, когато

конюнкцията

от входните

информационни

сигнали е

единица (RÇS=1). В

останалите

случаи се

превключва

според

таблицата за

истинност на

елементарен

RS-тригер с

право

управление.

Така в тази

схема

опасността

от

“забранена”

входна

комбинация (R=1, S=1) е

напълно

отстранена.

Показаните

на фигури 3.1.12 и 3.1.13

тригери от

тип S-, R-, и E- имат

условното

графично

означение

като на

тригерите от

фигура 3.1.4. Това

естествено

би ги направило

абсолютно

неразличими

по тяхното

УГО както по

функциониране,

така и по

вътрешна логическа

структура,

ето защо ако

УГО трябва да

бъде докрай

прецизно,

следва в

основното

функционално

поле

допълнително

да бъде

обозначен

типа на

тригера.

Преди

да

разгледаме

следващият

вид тригерна

структура, ще

се спрем на

следващите ненадеждни

тригерни

схеми, които

много

“авторитетни”

публични

издания

предлагат

върху Latch

тригерната

схема. Става

дума за JK- и

Т-тригери.

Логическите

схеми, които

читателят

може да срещне

са следните.

Фиг.

3.1.13-а. Синхронен

Latch

JK-тригер

и

асинхронен Latch

Т-тригер

Както

се вижда,

обединяването

на двата входа

J и K

на левия

тригер води

до схемата на

тригер Т,

показана в

дясната част

на фигурата.

В този

вариант тя е

асинхронна,

но ако входът

Т се означи

като С, а

вместо

константата

“1” се запише

името Т, то се

получава

логическа

схема на

синхронен Latch Т-тригер. В тази

схема

спокойно

може да бъде

премахната константата

“1”, а заедно с

това и

входовете на схемите

И, на които тя

е подадена.

Така стигаме

до

следващата

логическа

схема, която

ще подложим

на анализ.

Фиг.

3.1.13-б. Асинхронен

Latch

Т-тригер

Най-

напред ще

потвърдим, че

схемата се

превключва

според

логическото

уравнение на

Т-тригер.

![]()

Ще

направим

това при

условие, че

на вход Т постъпват

кратковременни

единични

импулси с

продължителност

достатъчна

за да превключат

тригерната

схема. Това

изказване е пълно

с неясни

термини (кратковременни,

достатъчна),

които ще

пренебрегнем

и ще

идеализираме

за сега. И

така,

процесът на

превключване

е изобразен

на

следващата

фигура.

Фиг.

3.1.13-в. Превключвания

в схемата на

асинхронния Latch

Т-тригер

Както

се вижда,

превключването

е правилно и

съответства

на

приведеното

по-горе уравнение,

т.е. след

всеки входен

импулс,

тригерът се

превключва в

противоположното

състояние.

Но, както

отбелязахме,

това е само в

идеалният

случай! На

практика продължителността

на входния

импулс Т не следва

да бъде

обвързана с

никакви

изисквания

от страна на

тригерната

схема. Това

не следва и

от

аналитичното

уравнение.

Нека си представим

една реална

ситуация, в

която датчик

генерира

единичен

импулс при

достигане на

горна мъртва

точка от

буталото в

един двигател.

Това (в

различни

варианти и

конструкции)

се налага,

когато

трябва да се

измерват

оборотите на

двигателя.

Логично е да

се съобрази,

че при високи

обороти

датчикът ще генерира

кратковременни

импулси. С

намаляване

на оборотите

обаче тези

импулси ще стават

все

по-широки, т.е.

по-продължителни.

В общия

случай това

означава, че

продължителността

на входните

единични

импулси може

да бъде

различна и

много

продължителна.

Нека сега

разгледаме

функционирането

на въпросната

логическа

схема именно

в условията на

много

продължителни

входни

импулси. За да

бъдем

пределно

ясни, ще

поясним, че “много

продължителни”

означава

много

по-продължителни

от времето за

превключване

на

тригерната

схема! Функционирането

на схемата

във времето

ще изобразим

с

времедиаграма.

Фиг.

3.1.13-г. Превключвания

в схемата на

асинхронния Latch

Т-тригер

Както

се вижда, по

причина на

обраните

връзки, в

тригерната

схема се

пораждат

вътрешно

схемни

състезания и

тя се превръща

в генератор

на

правоъгълни

импулси със

собствената

си

резонансна

честота. Така

се

обезсмисля

функционирането

на схемата

като тригер. Крайният

извод след

всичко

казано до

тук, който

читателят

следва добре

да осмисли е,

че във всяка

логическа

схема, в която

има обратни

връзки, могат

да се възбудят

вътрешно

схемни

състезания,

които да опорочат

нейното

функциониране

според логическите

уравнения по

които е

синтезирана.

По-задълбоченият

коментар на

този факт изисква

да се обърне

внимание на

логическото

уравнение на

тригера.

Научният

анализ на

схемата

следва да

изхожда от

теорията на

крайните

автомати, в

чието

фундаментално

въведение е

заложено

понятието “обратна

връзка”.

Именно

обратната

функционална

връзка от изход

на вход

изразява

зависимостта

на изходната логическа

стойност от

входната, или

с други думи, всяко

ново

състояние на

крайния

автомат е функция

от

предходното.

За да

функционира

на практика

техническото

решение на

подобни

логически

функции, в теорията

на крайните

автомати се

въвежда понятието

“дискретно

време” или

още “такт”. В

резултат на

това

логическите

функции се

изразяват с

времеви

уравнения, в

които е задължително

вписването

на времевата

зависимост.

Времето е

неявен

аргумент в

такива логически

уравнения,

ето защо то е

изразено във

функцията на изхода

като горен

индекс – Q(t). На

практика,

времевата

зависимост

изисква в

обратните

връзки на

логическата

схема да се

въведат

елементи на задръжка

(закъснение).

Така се стига

до

двутактовите

или още

двуетажните

тригерни

схеми, които се

разглеждат

под следващото

по-долу

заглавие.

Казаното

по-горе се

отнася в

пълна степен

и до

логическата

схема на

синхронния Latch JK-тригер, представен

на фигура 3.1.13-а.

За да

избегнат самовъзбуждането

на тези

тригерни

схеми, авторите

им често

предлагат

управление с

пулс-генератор,

което ние

разкритикувахме

и не препоръчваме

на читателя.

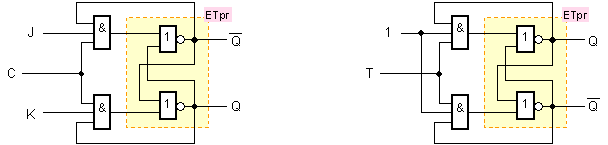

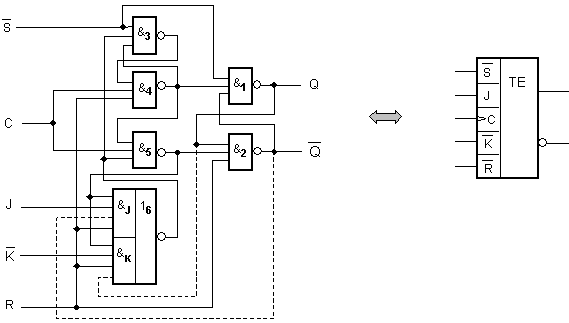

Тригери

със

структура Master-slave

Следващите

два тригера,

които ще

бъдат разгледани,

според

класификацията

за вида на информационните

входове се

наричат Т-тригер

и JK-тригер. По

силата на

своя

теоретичен

синтез те

имат вътрешна

логическа

структура,

която се

характеризира

с

въвеждането

на допълнителни

обратни

връзки от

изходите към

входовете,

както е

показано на

фигура 3.1.1.

Такова

въвеждане на

обратни връзки

в

логическите

схеми е едно

положение,

което в

повечето

случаи води

до вътрешно-схемни

състезания в

превключванията

на отделните

логически

елементи, а от

там до

превръщане

на цялата

схема в генератор.

Когато това

не е желано,

(освен в

случаите,

когато това

положение не

се преследва нарочно),

то в пълна

степен

следва при

проектирането

на такива

схеми да се

взема под внимание

концепцията

за времето,

което е

дискретно. В

резултат на

логическия

синтез в тези

случаи се

получават

така наречените

времеви

логически

функции, в

които

дискретното

време се

явява неявен

аргумент и

без него не

може да бъде

описано

функционирането

на

реализираните

по тези

уравнения

логически

схеми.

Реализацията

на

дискретното

време в

тригерните

схеми се

постига чрез вътрешни

закъснения

или чрез

външно многофазно

тактуване,

нещо което е

било обект на

научни

дискусии в

ранните

години на

развитието

на компютърните

науки.

Тъй

като

тригерните

логически

структури с

вътрешни

закъснения

имат чисто

теоретическо

положение и в

практиката

почти не се прилагат

(с много

малки изключения,

за които може

да бъде

прочетено в книга [5]), в

настоящата

книга ще

бъдат

разгледани

само тактово

управляваните

структури,

носещи

наименованията

Master-slave

и Edge.

На

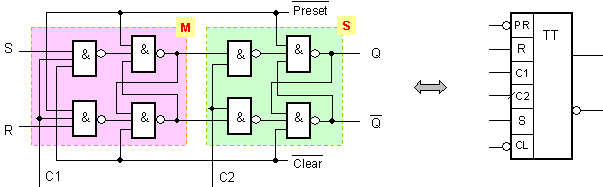

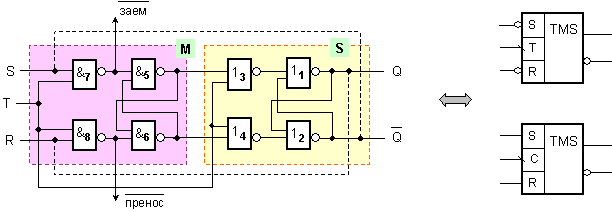

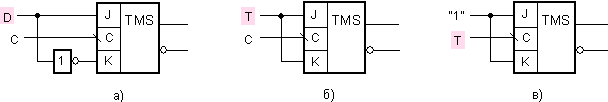

фигура 3.1.14 е

представена

принципната

логическа

схема на

двутактен

(С1,С2) синхронен

RS-тригер,

реализиран в

логическия

базис И-НЕ

(припомнете

си фигура 3.1.4).

Новото състояние

на тригера се

появява на

изхода Q с

появата на

втория

управляващ

сигнал С2, т.е. по

неговия

преден фронт.

В

логическата схема

са включени и

входове за асинхронно

инверсно

установяване

на тригера

чрез

сигналите Preset и Clear. В

логическата

структура на

тригера

съвсем

условно са

оградени с

пунктирна

линия съответно

основният

RS-тригер,

означен с

буква М (Master)

и

допълнителният

RS-тригер,

означен с

буква S (Slave).

Представената

структура

обаче все още

не може да

се определи

като

MS-структура,

тъй като двата

тригера се

тактуват

разделно от

два различни

сигнала (С1, С2).

Фиг.

3.1.14. Двутактен,

двуетажен,

синхронен

RS-тригер (логическа

схема и УГО)

Както

може да се

види от

фигура 3.1.14, УГО

на този

тригер

съдържа в

основното

функционално

поле

мнемоничния

код на

двутактовата

структура -

съчетанието ТТ.

За правилно и

надеждно

функциониране

на схемата

конюнкцията

от тактовите

сигнали

трябва да

бъде вечна

нула – (C1ÇC2)=0.

По-долу

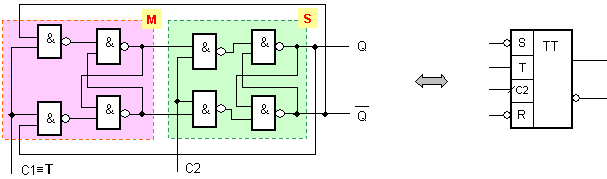

на фигура 3.1.15 е

показана

логическа схема

на Т-тригер,

който се

определя

като двутактен,

двуетажен,

асинхронен

тригер. Схемата

е построена

от два

последователно

поставени

елементарни

синхронни

RS-тригера с

право

управление,

реализирани

с логически

елементи И-НЕ

(виж фигура 3.1.4),

обхваната от

обратни

връзки.

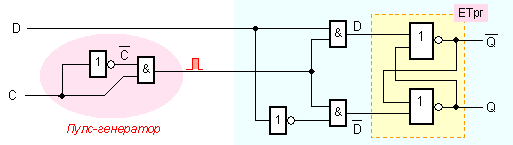

Фиг.

3.1.15. Двутактен,

двуетажен,

асинхронен

Т-тригер (логическа

схема и УГО)

За

сведение на

читателя

следва да отбележим,

че структури,

подобни на

описаните

по-горе, се

изпълняват

още на базата

и на други

елементарни

тригерни

схеми. Като

многотактни

могат да

бъдат

синтезирани

всички

типове

тригерни

схеми,

включени в

класификация

№2.

Изобразената

тригерна

схема с обратните

връзки е

защитена от

вътрешни лавинообразни

превключвания

чрез разделното

(двутактово)

записване

на

информация в

левия

елементарен

тригер, означен

като

“господар” – М, от

записването

в десния

елементарен

тригер,

означен като

“слуга” – S,

съответно чрез

управляващите

сигнали С1 и С2,

чиято конюнкция

трябва да

бъде вечна

във времето константа

нула, т.е. (С1ÇС2)=0,

според

концепцията

за

дискретното

време.

Благодарение

на

кръстосаните

обратни връзки,

управляващият

сигнал С1

играе ролята

на броячен

вход (С1ºТ), при

което се

постига

известната

времева логическа

функция на

тригера:

![]()

където с t е означен

номерът на

текущия

времеви такт.

Параметърът t е цяло

число, което

представлява

неявен и нелогически

аргумент на

логическата

функция.

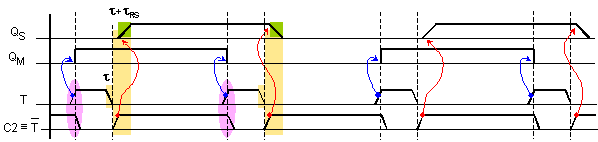

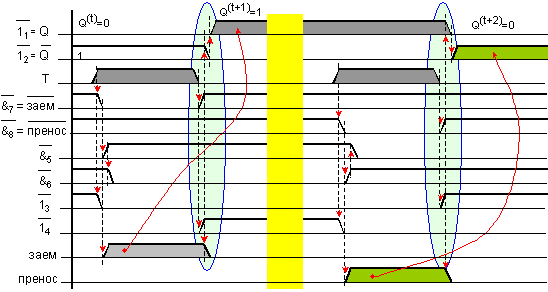

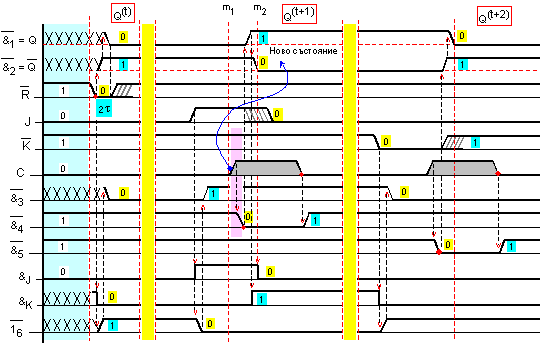

Времедиаграмата

за

превключване

на тригерната

схема от

фигура 3.1.15 е

представена

на фигура 3.1.16.

Както може да

се види върху

нея, изходът

на тригера

![]()

се

превключва в

противоположно

състояние по

предния

фронт на

всеки тактов

импулс С2.

Входният

импулс Т се

регистрира

във входният

RS-тригер, но

новото

състояние

![]() ,

,

което

той е

формирал

според

представеното

по-горе

уравнение,

остава

запомнено в Master-тригера.

Това

състояние не

излиза на

изход, докато

не пристигне

следващият

преден фронт

на импулса С2.

Фиг.

3.1.16. Превключване

на двутактен

асинхронен

Т-тригер

Логическа

структура,

която обаче

носи наименованието

Master-slave (MS) се

получава,

когато

вторият

управляващ сигнал

С2 се формира

като

инверсен на

първия, т.е.

С2=![]() .

.

Този

начин на

получаване

на втория

управляващ

сигнал (чрез

дефазиране

на първия управляващ

сигнал в

двутактните

схеми) подвежда

тригерната

схема под

наименованието

с

вътрешно

закъснение.

Това е така,

защото

новото

състояние на

тригера

излиза на

изход след

края, т.е. след

изчезването

на първия

управляващ

сигнал. Споменатата

по-горе

конюнкция от

двете фази на

управляващите

структурата

сигнали теоретично

отново ще

бъде

константа

нула

![]()

Искаме да

предупредим

читателя, че в

някои

литературни

източници

получаваните

по този начин

тригерни

схеми се

наричат

“еднотактни”,

което според

нас е

погрешно и

води до

заблуждение,

тъй като

двуетажните

структури по

принцип не

могат да

бъдат

еднотактни в

смисъла на

своето логическо

превключване.

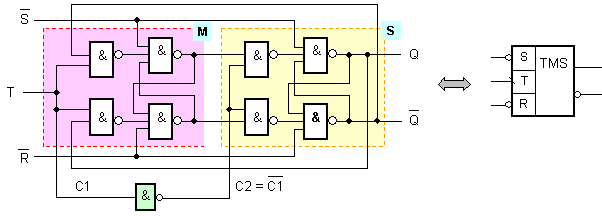

Окончателната

логическа

схема на MS

Т-тригера,

допълнена с

приоритетните

установъчни

входове

![]()

е

представена

на фигура 3.1.17.

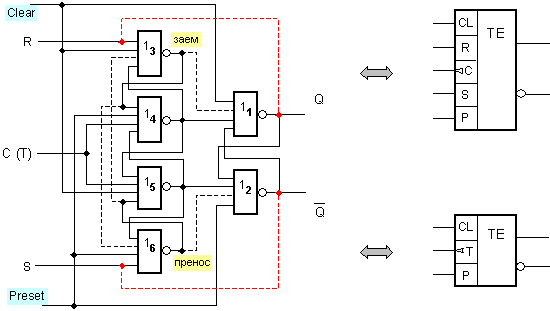

Фиг.

3.1.17. Т-тригер

с вътрешно

закъснение,

тип Master-Slave (логическа

схема и УГО)

Превключването

на

Т-тригерът,

т.е. появата на

новото

състояние на

изхода му Q,

става в

момента на

задния фронт

на входния

импулс Т, което в

УГО е

показано

чрез дясно

наклонения

указател на

информационния

вход (при

този тригер

Т-входът се

приема за

информационен,

тъй като

постъпващите

по него

импулси определят

изходното

състояние,

според логическата

функция,

посочена

по-горе). С

въвеждане на

допълнителни

схеми И към

входовете R и S

на Master-тригера

и

допълнителен

управляващ

сигнал С, може

да се получи

синхронен

Т-тригер,

който не

показваме и

оставяме

неговия

синтез на

читателя.

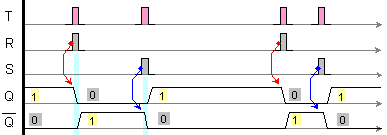

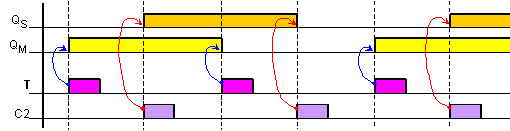

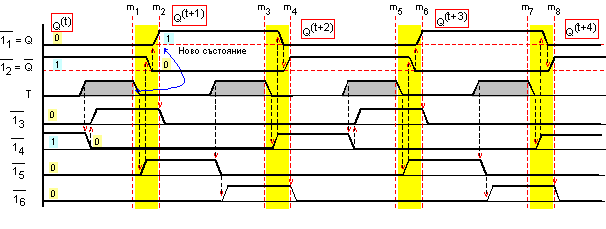

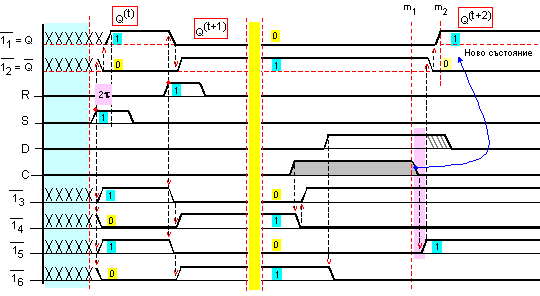

Времедиаграмата

за

превключване

на Т-тригера

от фигура 3.1.17 е

представена

на фигура 3.1.18, в която,

за да стане

възможно

неговото

анализиране

и

формулиране

на

съответните

изводи, са изразени

явно и

подсилено

фронтовете

на импулсите.

Фиг.

3.1.18. Превключване

на

асинхронен MS

Т-тригер с

вътрешно

закъснение

Това

което може да

се види на

фигура 3.1.18 е, че

всяко ново

състояние на

тригера се

установява

след изчезване

на входния Т

импулс, след

време, което

е равно на

сумата от

продължителността

на предния

фронт на импулса

![]()

плюс

времето за

превключване

на

допълнителния

изходен

RS-тригер,

както е означено

на

времедиаграмата

така

![]()

В този

смисъл се

говори, че

тригерът се

превключва

по задния

фронт на

входния

сигнал.

Дефазирането

на входния

тактов

сигнал Т чрез

логическо

инвертиране,

при което

инверсният

сигнал за

управление на

допълнителния

S-тригер се

получава

последователно

от входния, е

едно ненадеждно

схемно

решение, тъй

като при

влошени

технически

параметри на

дефазиращия

инвертор е

възможно

застъпване

във времето

на

фронтовете

на неговите

вход и изход,

в резултат на

което може да

се реализира

състезание

по обратните

връзки в

логическата

схема и

крайното състояние

на тригера да

се окаже

неизвестно.

Ето защо

показаната

на фигура 3.1.17

логическа

схема е

по-скоро

теоретична

отколкото практическа.

Практическите

MS структури

имат други

схемни

решения, две

от които ще

покажем тук.

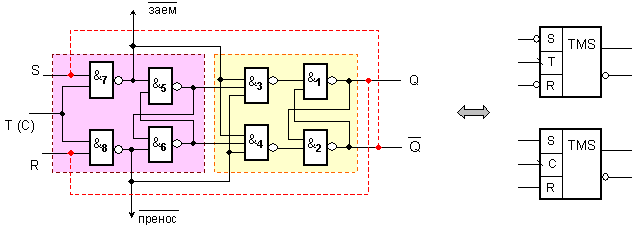

Първото

решение на MS

структурите

се

характеризира

с въвеждането

на вътрешни

връзки, забраняващи

записа в

спомагателния

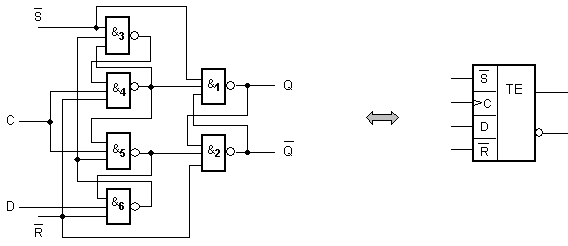

тригер. На

фигура 3.1.19 е

показана логическа

схема, която

съвместява

изобразяването

на две

различни

тригерни

структури едновременно:

на

асинхронен

Т-тригер и на

синхронен

RS-тригер,

синтезирана

на базата на

логически

елементи

И-НЕ.

Аналогично,

подобна

тригерна

схема може да

се синтезира

на базата на

елементи

ИЛИ-НЕ, но тя

ще се

превключва

от

инверсната

стойност на

входния управляващ

сигнал

(схемата не

показваме и

оставяме

синтеза и

изследването

й на

читателя).

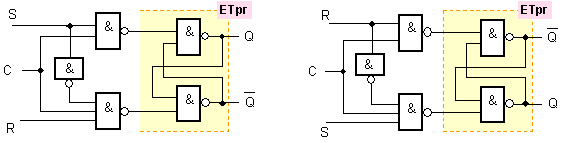

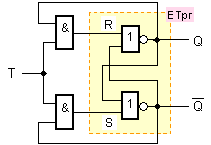

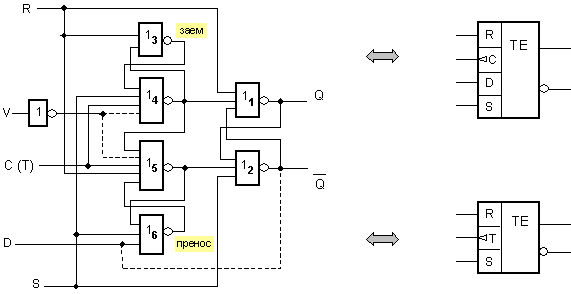

Фиг.

3.1.19. Асинхронен

MS Т-тригер и

синхронен MS RS-тригер

със забраняващи

връзки

Приоритетните

инверсни

входове за

установяване

на

тригерната

схема тук не

са изобразени,

но те са

аналогични

на

показаните на

фигура 3.1.17. В

УГО на

Т-тригера

обаче те са

показани.

Обратните

връзки в

логическата

схема от фигура

3.1.19, които

всъщност

реализират

Т-тригера, са

показани с

пунктирна

линия. Освен

това са

показани

бързодействащите

изходи на тригера

за “пренос” и

за “заем”,

които се

използуват

при

включването

му в

многоразрядни

броячни

схеми. Поради

това, че

функциите за

пренос и за

заем се

генерират в

инверсна

стойност,

включването

им към

Т-входовете

на съседните

разряди в

броячните

схеми, ще

изисква

допълнителен

инвертор.

Този недостатък

може да бъде

отстранен

при подходяща

логическа

база, което

оставяме

като задача

на читателя.

Когато

обратните

връзки в

разглежданата

схема

отсъстват, а

входните

логически

схеми И-НЕ са

допълнени,

както е

показано, с S и R

входове,

тригерната

схема

представлява

синхронен

RS-тригер, тип MS

със

забраняващи

връзки и

тогава

входът Т следва

да се означи

с буква С,

както е

показано в

долното УГО

на фигура 3.1.19.

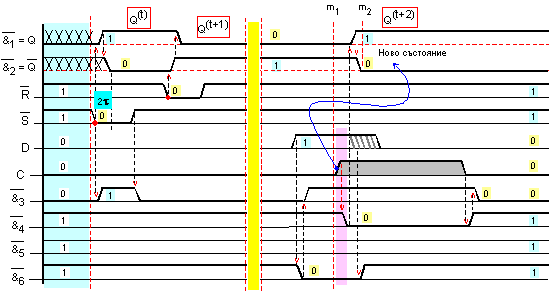

На

фигура 3.1.20 е

показана

времедиаграмата

на превключването

на описвания

по-горе Т-тригер,

при начално

състояние

![]()

Отново,

както за

тригера от

фигура 3.1.17, може

да се твърди,

че

превключването

и на този

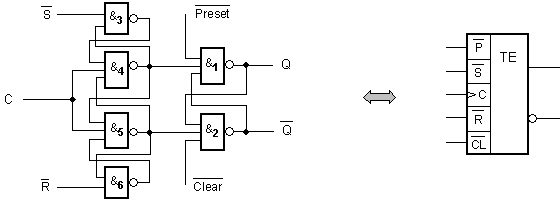

Т-тригер е по

причина на

задния фронт

на входния

импулс, при

което новото

му състояние

се

установява

след

закъснение

от 4 последователни

фронта (4.t) на

градивни

логически

елементи.

Новото състояние

според,

логическата

функция на

Т-тригера, е

противоположното

на

предидущото

и то се

съхранява

неограничено

дълго във

времето, до

следващия

входен

импулс.

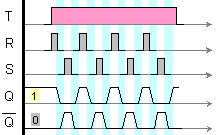

Фиг.

3.1.20. Превключване

на

асинхронен MS

Т-тригер със забраняващи

връзки

След

появата на

единичния

импулс на

Т-входа, входовете

на изходния

елементарен

RS-тригер,

образуван от

логическите

елементи

![]()

получават

неактивната

за него

комбинация,

т.е. неговото

превключване

е забранено,

но не от

инвертираната

фаза на

входния

импулс, както

беше в

схемата от фигура

3.1.17.

Изключително

ценното в

тази логическа

схема е

изпреварващото

формиране на

импулсите за

“пренос” и

“заем”.

Въпреки че в

схемата те се

формират в

обратните си

стойности, на

времедиаграмата

за улеснение

са

представени

и техните

прави

стойности.

Вижда се, че в

съответствие

на изходния Q-импулс

(и съответно

в

съответствие

на изходния not(Q)-импулс),

изпреварващо

във времето,

равно на

продължителността

на входния

Т-импулс, се

формира

импулс на

изхода “пренос”

(съответно на

изхода “заем”).

Тези изходи могат

да се

използуват

при синтез на

броячи с

повишено

бързодействие.

Времето

за

превключване

на

тригерните

схеми със

забраняващи

връзки може

да бъде намалено

чрез

намаляване

на броя на

логическите

инвертори. За

целта при

синтеза на

логическата

схема трябва

да се

използуват

различни

логически

базиси за

логическите

елементи на

елементарните

тригери. Този

подход е

показан на

фигура 3.1.21,

където

основният

елементарен

тригер е в

базиса И-НЕ, а

допълнителният

– в базиса

И-ИЛИ-НЕ.

Тригерната

схема отново

показва

съвместно

изобразяване

на два тригера

– асинхронен MS

Т-тригер със

забраняващи връзки

и синхронен MS

RS-тригер със

забраняващи

връзки.

Обратните

връзки в

схемата са изобразени

с пунктирни

линии. И в

тази схема, в

случай, че

бъде

разглеждан

Т-тригер, са

показани

бързодействащите

изходи на функциите

за “пренос” и

за “заем”,

които се

използуват

при синтез на

многоразрядни

броячни

схеми.

В

логическата

схема на

фигура 3.1.21 не са

изобразени

приоритетните

установъчни

входове на

тригера,

чийто синтез

отново

оставяме на

читателя.

Обясненията,

касаещи

изобразените

на тази

фигура УГО,

съответстват

по

аналогичен

начин на

изложените

на фигура 3.1.19.

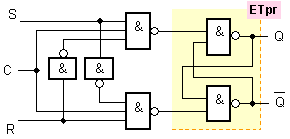

Фиг.

3.1.21. Т-тригер

и RS-тригер със забраняващи

връзки и

различни

логически

елементи

Построяването

и

изследването

на времедиаграмата

за

превключване

на

представената

на фигура 3.1.21

тригерна

схема

оставяме като

задача на

читателя.

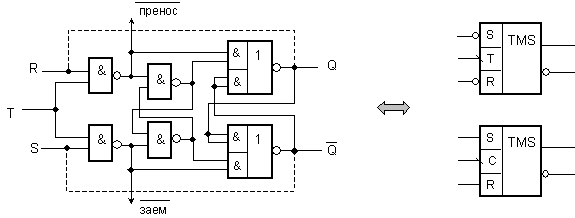

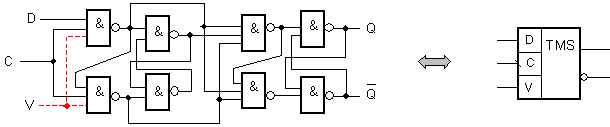

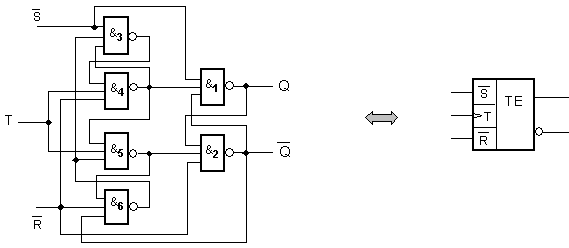

Второто

решение на MS

структури,

което

показваме

по-долу, се

характеризира

с използване

на две различни

функционално

пълни

системи от

елементарни

логически

функции за

реализация

на основния и

на

допълнителния

тригери,

например И-НЕ

и ИЛИ-НЕ. Едно

такова

решение е

показано на

фигура 3.1.22,

където основният

тригер е

реализиран в

системата от

логически функции

И-НЕ, а

допълнителният

– в системата

ИЛИ-НЕ. При

включени

обратни

връзки,

тригерът е

асинхронен,

от тип Т и

входовете S и R

не бива да

съществуват.

В случай, че

обратните

връзки не

съществуват,

тригерът е

синхронен, от

тип RS и входът Т

следва да се

означи с

буква С – като

вход за

управление

на записа.

За

читателя би

представлявал

интерес анализът

на

логическата

схема на

представените

по-долу

асинхронен MS

Т-тригер и

синхронен MS

RS-тригер,

когато

основният (M)

тригер бъде

реализиран в

системата

ИЛИ-НЕ, а

допълнителният

(S) – в системата

И-НЕ.

Вече е

пределно

ясно, че

анализът на

тригерните

схеми се

извършва

върху

времедиаграмата

на тяхното

превключване,

ето защо за да

улесним

читателя, а и

за да бъдем

последователни

в

обясненията,

ще

представим

на фигура 3.1.23

времедиаграмата

за

превключването

на

асинхронният

Т-тригер със

забраняващи

връзки и

различни

логически

базиси от варианта,

чиято

логическа

схема е

представена

на фигура 3.1.22.

Фиг.

3.1.22. Асинхронен

MS Т-тригер

(синхронен MS

RS-тригер) в различни

логически

базиси

Фиг.

3.1.23. Превключване

на

асинхронен MS

Т-тригер със

забраняващи

връзки

и

елементарни

тригери в различни

логически

базиси

От

фигурата се

вижда, че

времедиаграмата

в голяма

степен

прилича на

изобразената

преди това на

фигура 3.1.20. Това

не е

случайно, тъй

като

принципът, по

който са

построени

съответните

тригерни

схеми, е един

и същ, а

именно схеми

със

забраняващи

връзки. В

схемата от

фигура 3.1.22

забраната

върху

изходния елементарен

тригер се

постига

директно от входния

Т импулс, тъй като

този тригер е

с инверсно

управление,

синхронизиран

инверсно (това

схемно

решение

читателят

може да си припомни

от фигура 3.1.5).

Останалите обяснения,

свързани с

превключванията

на коментираната

тригерна

схема,

съвпадат с онези,

които бяха

направени

при

разглеждане

на

времедиаграмата

от фигура 3.1.20.

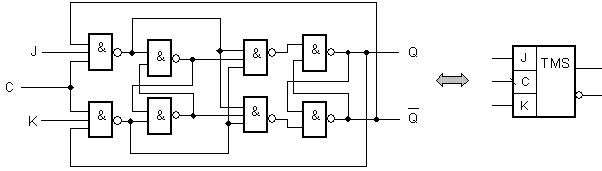

В

съответствие

с изложените

MS логически

структури

могат да

бъдат

синтезирани

не само Т и RS тригерите,

но D

и JK

тригерите. На

фигура 3.1.24

например, е

представена

MS

структурата

на D-тригер

със

забраняващи

връзки. С

пунктир е

показана

възможността

за включване

на V-вход.

Фиг.

3.1.24. Синхронен

MS D-тригер със забраняващи

връзки

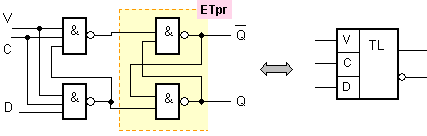

На

фигура 3.1.25 е

представена

MS

структурата

на JK-тригер

със

забраняващи

връзки.

Фиг.

3.1.25. Синхронен

MS JK-тригер със забраняващи

връзки

Без

да

представяме

останалите

схемни варианти

в

подробности,

използвайки

УГО на вече

разгледаните

тригери, по-долу

ще

представим Master-slave

тригери от

тип D и JK, които

могат да

бъдат синтезирани

като

двутактни

(според

фигури 3.1.14 и 3.1.15), по

схемата с

вътрешно

закъснение

(според фигура