ГЛАВА 2

Микроконвейерни звена

Micro-pipeline stages

В тази глава е изложено и приложено едно ново

разбиране относно възможността за организация на управлението на операционни

(изчислителни) структури. Това разбиране дава възможност за нов подход при

създаване на хардуерни устройства и системи, който се характеризира с това, че

изключва необходимостта от синтез на крайни автомати за управление. Синтезът на

управляващ автомат не се съдържа като етап в методиката за проектиране на

операционните структури нито във варианта с апаратно закрепена логика, нито във

варианта с програмно закрепена логика. Новата концепция се основава на

събитийността и причинно следствените връзки при функциониране на структурите.

Те от своя страна са изразени в алгоритмите, реализацията на които се търси в

така пояснените условия, при това във вариант, обезпечаващ възможно най-голяма

производителност. Високата производителност се постига чрез осигуряване на

възможност за естествена реализация на различни форми на паралелизъм, главната

от които е конвейерната.

Предложеният подход може да бъде прилаган при синтеза както на синхронно работещи, така и на асинхронно работещи операционни структури. Основното му достойнство се състои в опростяване и хомогенизиране на апаратурата, както и във възможността за значително повишаване на изчислителната производителност чрез нейната конвейеризация. Възможността за конвейерна организация на всички основни алгоритмични структури актуализира задачата за апаратна реализация на възможно най-общ по структура изчислителен процес.

Въз основа на новата концепция са синтезирани

различни апаратни структури, които реализират циклически алгоритмични

структури. Циклическата алгоритмична структура е най-сложната и като основен

градивен елемент е актуална със своята висока честота на използване.

Освобождаването на нейната апаратна реализация от класическия управляващ

автомат определено е положителен резултат. Синтезираните хардуерни структури се

определят като конвейерни звена, тъй като имат необходимите външни връзки и

начин на взаимодействие със себеподобните си. Синтезираните микроконвейерни

звена са определени като многотактови. Различават се обаче като такива и с еднотактово и с многотактово циклическо тяло.

Представените в тази глава звена са синхронни. Всички представени структури

функционират под въздействието на еднофазова тактова последователност.

Изследвани са решения, използващи логически възли, които функционират както по

преден, така и по заден фронт, при това в различни възможни комбинации от

практически реализации. Решенията се отнасят за различни по вид цикли.

Тъй като в управлението си, синтезираните

операционни структури не зависят от същността на циклическото тяло, те могат да

бъдат разглеждани като методи за хардуерна реализация на съответните

алгоритмични структури.

2.1. Операционни структури с управление без

крайни автомати. Предпоставки за микроконвейерна организация на управлението

Проектирането

на цифрова апаратура в съвременни условия съществено се различава в сравнение с

проектирането в недалечното минало. Това се дължи както на новите градивни

елементи и техните възможности, така и на развитите програмни средства за

автоматизация на проектирането. Благодарение на тази еволюция на технологиите

като цяло стават възможни за реализация такива подходи и методи, като този,

който е представен по-долу. Той се характеризира с нова организация на

изчислителния процес, даваща възможността за апаратна реализация на различни

форми на паралелизъм в логическите (числените) изчисления.

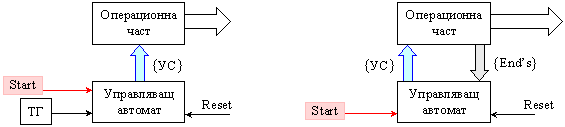

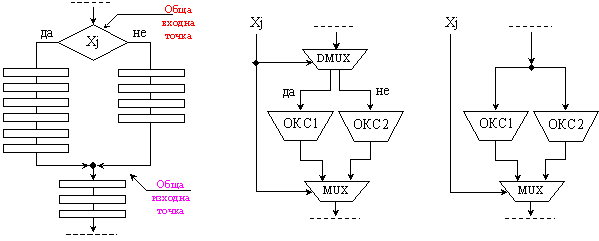

2.1.1. Традиционна постановка

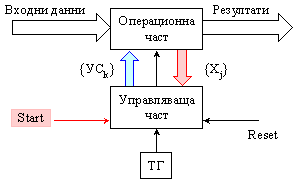

Разглеждаме класическата

представа за логическа структура на изчислителен автомат, според

декомпозиционния модел на В.М. Глушков – фигура 2.1.1.

Фиг. 2.1.1. Представа за логическа структура на

устройство

Както се вижда, структурата

съдържа две основни части:

§

Първата се нарича операционна, тъй като тя съсредоточава всички

логически възли и връзки между тях, които са необходими за преработката на

входните данни по точно определен алгоритъм. Именно този алгоритъм се използва

при синтеза на тази част. В резултат на изпълнението на последователността от

микрооперации в отделните възли на операционната част на устройството, се

получават изходните резултати;

§

Втората част се нарича управляваща. Тя е синтезирана като краен

автомат, който, издавайки в определена последователност управляващи сигнали {УСk}, k=1,2,3,…,M, към операционната част, реализира алгоритъма за

обработка на данните. По време на управлението, при необходимост, алгоритъмът

за управление използва стойностите на множество оповестяващи сигнали {Xj},

j=1,2,3,…,N. Така управляващата част всъщност съдържа в себе си алгоритъма за

управление. С букви M и N е означена мощността на съответните множества.

Когато за

превключване на управляващата част на устройството се използва тактов генератор

ТГ, устройството се определя като синхронно. Този метод за управление се

определя още като синхронен. Функционирането на представената структура може да

бъде организирано и чрез метода на асинхронно управление, както и чрез някаква

тяхната комбинация. В случай на асинхронно управление тактовият генератор

липсва като елемент в структурата за сметка на допълнително множество сигнали

от типа ”край на микрооперацията” {End’sq}, q=1,2,3,…,L, както е показано на

фигура 2.1.2. Сигналите от последното множество се използват фактически за

причиняване на всяко следващо превключване в операционната част на

устройството. Всяка микрооперация, която е стартирана чрез управляващ сигнал,

трябва да генерира в отговор свой собствен сигнал от тип “край на

микрооперацията”, който ще бъде причина за следващото превключване на

управляващия автомат.

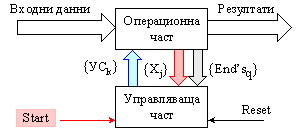

Фиг. 2.1.2. Допълнителни сигнали при асинхронно

управление

И в двата метода на

управление устройството обикновено се намира в изходно (начално) състояние и

изпълнява функциите си след подаване на външен сигнал, формално означен “Start”.

В изходно състояние то фактически очаква този сигнал.

Характерно за класическите

(традиционните) реализации е това, че управляващата част на структурата

реализира управляващия алгоритъм на ниво микрооперации като краен автомат с

апаратно закрепена логика или като такъв с програмно закрепена логика. Методиките

за синтез на синхронни и на асинхронни управляващи автомати са добре познати от

литературата, например от книги [1], [2] и [3], представени на

този сайт.

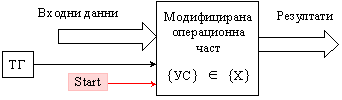

Тук в това встъпление

искаме да покажем, че основните алгоритмични структури, които могат да се съдържат

в управляващия алгоритъм, и които се реализират технически (апаратно или

микропрограмно) в управляващата част на устройството, могат да бъдат

прехвърлени (вградени) в операционната му част. Формално това може да се изрази

чрез принадлежността на управляващите сигнали към множеството на оповестяващите

сигнали. С други думи, основавайки се на причинно следствените връзки, имаме

право да разглеждаме управляващите импулси, като причинители на превключванията

и възникващите в резултат на това признаци, като сигнали на едно и също

множество. При постигане на тази цел, в изчислителната структура остава

единствено модифицираната операционна част, получена в резултат на съответното

преобразуване на управляващата част.

Разбирането ни за

крайния резултат е представено на фигура 2.1.3.

Фиг. 2.1.3. Окончателен вид структурата на устройство

без автоматно управление

Структурата може да бъде

както синхронно, така и асинхронно управлявана. Основният ефект от възможността

за постигане на изказаната цел е премахването на самостоятелното съществуване

на управляващата част и нейното прераждане в своеобразни форми, интегрирането

на които в операционната част се постига в резултат на прилагане на определени

правила. Тази възможност ще дискутираме по-долу.

2.1.2. Основни алгоритмични структури

Изхождайки от

теоретичното положение, че управляващата част на операционното устройство се

синтезира в пълно съответствие с алгоритъма за неговото функциониране, нашият

обект за изследване тук са основните алгоритмични структури, които могат да се

срещнат в него.

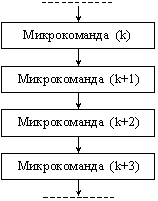

Линейна алгоритмична структура. Линеен микроконвейер.

Линейната алгоритмична

структура, която е илюстрирана на фигура 2.1.4, се организира с помощта на

безусловни алгоритмични преходи от вида “на следващия по ред”. Тези преходи са

задължителни и се изразяват чрез стрелки, изразявайки по този начин единствено

възможния ход на изчислителния процес.

Фиг. 2.1.4. Линейна алгоритмична структура

Структурата представлява последователност

от микрокоманди (съвкупност от управляващи сигнали, подавани в един и същи

такт), които се изпълняват последователно в операционната част на

изчислителното устройство. Всеки управляващ сигнал, като част от

микрокомандата, възбужда съответната микрооперация в съответния логически

възел.

Разбирането ни за

функциониране на управляващата част се изразява в следното: управляващата част

функционира като извършва последователни превключвания от едно вътрешно

състояние в друго строго определено вътрешно състояние. Тези превключвания се

осъществява под въздействието на последователните тактови импулси или на

асинхронните сигнали от типа “край на микрооперацията”. Така традиционната

реализация на изчислителното устройство може да се представи по начин, показан

на фигура 2.1.5.

Фиг. 2.1.5. Схеми за реализация на изчислителния

процес

Разбирането, което изразява

горната рисунка е, че главен двигател на изчислителния процес в структурата е

тактовия генератор, или множеството сигнали {End’s}. Множеството на

оповестяващите сигнали {X} не е показано.

Функционирането на

управляващия автомат в горната структура, както вече беше казано, представлява

процес на превключване от състояние в състояние, при което в различни точки на

операционната част, за кратко време (един такт) се подават различни управляващи

сигнали. Изходът на този управляващ автомат представлява множество от изходни

линии {УС}. Нашето разбиране за управляващ сигнал е, че той представлява

правоъгълен импулс. Що се отнася до входа, при метода на синхронно управление

той представлява една единствена линия, по която постъпват импулсите на

тактовия генератор ТГ.

При метода на асинхронно

управление управляващият автомат има множество от входни линии, по които

постъпват сигналите от множеството за край на превключването {X}. И в двата

случая, както вече беше казано, всичко започва с появата на асинхронния сигнал Start.

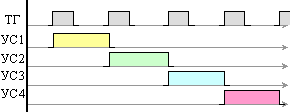

Ходът на изчислителния

процес във времето се представя обикновено с времедиаграма (фигура 2.1.6). Тя

изразява логиката на процеса чрез превключванията на логическите елементи в

схемата. По тази причина времедиаграмата е единственото средство, което може да

докаже работоспособността на всяка логическа схема.

Фиг. 2.1.6. Времедиаграма на процеса управление в

линеен участък

Представен по този начин,

възприемането на управляващия автомат е като за своеобразен разпределител

(превключвател или мултиплексор), през който минават тактовите импулси,

появявайки се в различни точки на операционната част на структурата, но по един

единствен път (във времето, както е показано на фигура 2.1.6). В зависимост от

условията, налагани от градивните елементи в операционната част, тези импулси

могат да са синхронни с правата или с инверсната фаза на тактовата

последователност, да имат продължителността на периода, на единичната или на

нулевата стойност в сигнала. Не изключваме и необходимост от по-продължителни

въздействия.

Изхождайки от това

разбиране стигаме до извода, че управляващият автомат може да бъде премахнат от

структурата чрез подходяща модификация на операционната част. Не е трудно да се

осъзнае, особено когато се наблюдава фигура 2.1.6, че същността на тази

модификация се състои в нейната конвейеризация. Ще поясним това твърдение с

примера от фигура 2.1.4, която изобразява последователност от 4 управляващи

сигнала. При положение, че в четирите последователни микрокоманди се подават

четири различни управляващи сигнала, които възбуждат 4 различни микрооперации,

то операционните схеми, които ги реализират, са комбинационни схеми, 4 на брой

и са различни. Те са последователно разположени, при което ще предават

резултатите си също последователно, една на друга. Така естествено стигаме до

идеята за формиране на 4-степенна линейна конвейерна структура, която е

показана на фигура 2.1.7.

Фиг. 2.1.7. Линейна конвейерна структура

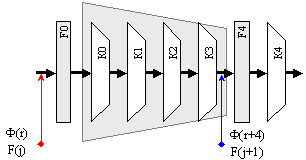

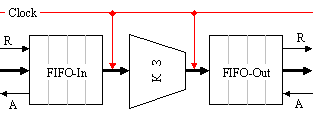

В структурата се виждат

конвейерните регистри (регистри фиксатори) Ф0, Ф1, Ф2, Ф3 и Ф4, чието

предназначение е да поддържат във времето междинните резултати. Към изходите на

регистрите са включени комбинационни операционни схеми К0, К1, К2, К3 и К4,

реализиращи по същество микрооперационната логическа преработка на данните.

Съвкупността от регистър фиксатор и комбинационна операционна схема беше вече

определена като микроконвейерно звено. Следователно под микроконвейер ще

разбираме последователност от микроконвейерни звена.

Резултатите от преработката

на данните във всяко звено се явяват на изходите на комбинационните схеми и в

подходящия момент се записват в следващия регистър фиксатор. Тъй като

микрооперация запис на данни в регистър е активна микрооперация, тя се постига

чрез нарочно подавани управляващи сигнали УС0, УС1, УС2, УС3 и УС4. Тяхната

последователност съответства на алгоритъма, изразен чрез блок-схемата от фигура

2.1.4. Тази последователност е пренесена (е реализирана) в логическата

структура на конвейера чрез подходящото последователно подреждане на

микроконвейерните звена. Посоката на придвижване или още на хода на

изчислителния процес, която в блок-схемата се определя чрез алгоритмичните

преходи, в конвейера се указва чрез насочените даннови връзки.

Конвейерната структура се

характеризира с особен вид организация на функциониране, която се нарича също

конвейерна. Конвейерната организация на функциониране е особен вид паралелно

във времето функциониране на структурните елементи в конвейера. Функционирането

се определя като паралелно поради липса на функционални връзки, които да влияят

върху работата на отделните комбинационни схеми. При тази организация в

отделните степени конвейерът изпълнява изчислителен процес върху множество

задачи, но с различни начални данни. В конвейера тези задачи се намират в

различна степен на завършеност. Ако конвейерът има 4 степени, това означава, че

в него са заредени и се изпълняват 4 задачи. В един и същи момент в различните

степени на конвейера се изпълняват изчисления върху тези различни задачи.

Придвижването на задачите в конвейера е последователно от звено в звено при

спазване на реда.

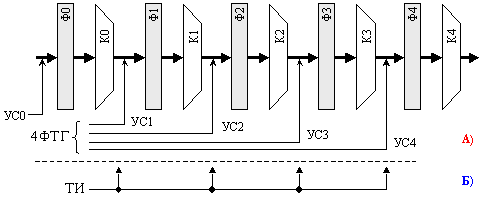

Основният параметър, характеризиращ

конвейерната структура, е оценката за неговата производителност, в сравнение с

последователното незастъпващо се във времето изпълнение на същия брой задачи. В

условията на линеен алгоритъм от m на брой такта,

получаването на резултат за една конкретна задача изисква същия брой тактове.

Тогава за последователното изпълнение на n задачи ще са

необходими ТП=(n.m)

на брой такта, ако приемем продължителността на един такт условно за

константа единица. Ако същият брой задачи биват последователно зареждани за

изпълнение в един m-степенен линеен

конвейер от вида, показан на фигура 2.1.7, необходимото време за тяхното

изпълнение ще се оцени така

![]()

Производителността Р ще оценим чрез

отношението на продължителностите на изчислителния процес за двата варианта

![]()

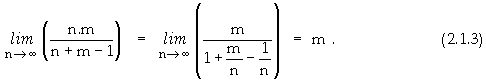

За горната оценка твърдим,

че има стойност, която клони към числото m, с нарастване на броя на изпълнените задачи

Резултатът (2.1.3)

означава, че m-степенната конвейерна организация е m пъти по-производителна от

последователната организация на изпълнение.

Управлението на

конвейерната структура изисква единствено подходящо тактуване, при което

резултатите, получени от едно звено, ще се предават като входни данни към

следващото звено. Това тактуване може да бъде реализирано като общо и

синхронно, с еднофазов тактов генератор (вариант Б) на фигура 2.1.7 или с

многофазов (4-фазов) тактов генератор 4ФТГ (вариант А) на същата фигура).

Синхронното управление може

да има разнообразни реализации, които зависят от вида на тригерите, изграждащи

регистрите фиксатори. Алтернативният вариант е асинхронно управление, което се

постига с различни конвейерни автомати.

След така изложения

коментар, премахването на явното управление на операционната част на

изчислителното устройство в лицето на управляващия автомат (вижте фигура

2.1.5), което беше смисъла на поставената цел, може да бъде постигнато чрез

премахване на междинните регистри и обединяване на оставащите комбинационни

схеми. Това преструктуриране представлява търсеното решение и то е илюстрирано

чрез фигура 2.1.8.

Фиг. 2.1.8. Преминаване към еднотактно изчисление

Премахването на съответните

фиксатори от конвейерната структура (в което всъщност се състои модификацията на

операционната част) води до пълно еднотактно комбинационно изчисление на

групата от последователни микрооперации. Оптимизацията на такъв тип

комбинационна схема е сериозно предизвикателство за синтез. Това решение

противоречи на зависимостта (2.1.3), която изисква увеличаване на броя на

конвейерните степени. Въпреки това обаче изложеното е полезно, защото показа,

че класическите схеми за управление имат алтернатива, която е сериозен

конкурент по всички направления. Типичен пример, който илюстрира казаното, са

схемните умножители или делители. Такива схеми читателят може да види тук в книги [1] и [3].

Условна

алгоритмична структура

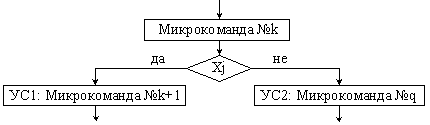

Условната алгоритмична

структура е втората основна структура. Тя се дефинира чрез условен алгоритмичен

преход, както е показано графично на фигура 2.1.9. Структурата се организира

чрез генерирано в операционната част условие (оповестяващ сигнал Xj),

чиято стойност в традиционното управление, се оползотворява като се проверява в

управляващия автомат.

Фиг. 2.1.9. Условна алгоритмична структура

Външно, за операционната

част ОЧ, същността на действието, което при това изпълнява управляващият

автомат УА, е избор измежду двата управляващи сигнала: да подаде УС1 или да

подаде УС2. Разбирането за апаратната реализация на управлението в този случай

е изобразено на фигура 2.1.10, в лявата й половина.

Фиг. 2.1.10. Самоопределяне на микрооперацията

Както за предидущата

алгоритмична структура, така и за тази разглеждаме възможности за управление,

алтернативни на класическото.

Задачата за премахване на

управлението (като част от управляващия автомат) в този случай решаваме

апаратно, както е показано в дясната половина на фигура 2.1.10. Алгоритмичният

избор, който управляващият автомат би следвало да направи, може лесно да се

реализира апаратно вън от него в една комбинационна схема КС, която реализира

двузначната дилема на избора и генерира алтернативните управляващи стойности

като функция от оповестяващия сигнал Хj. Именно тази възможност ни

води до извода, че управлението (в тази му част) се отнема от управляващия

автомат (както е показано на фигура 2.1.10), с което твърдим, че сме постигнали

поставената цел и в разглеждания случай.

Функционалността на

комбинационната схема КС (фигура 2.1.10) се определя и конкретизира в

зависимост от последващото алгоритмично развитие на двата клона на условната

структура. Възможностите в алгоритъма да се развият разнообразни структури,

засягащи разглежданата в случая конкретна структура, зависят от различните по

вид алгоритмични преходи. В крайна сметка тези възможности се свеждат до

няколко, които ще анализираме по-долу.

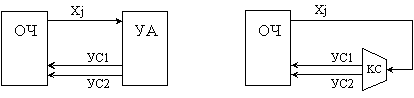

Първоначалната структура от

фигура 2.1.9 определя за комбинационната схема КС функционалността

демултиплексор, показан на фигура 2.1.10. На фигура 2.1.11 разглеждаме едно от

основните възможни развития на условната структура, което се характеризира с

два паралелни линейни участъка, обединяващи се в една обща точка.

В този случай, за постигане

на нашата цел можем да предложим две решения. Решенията съдържат два паралелни

конвейеризирани линейни участъка, във вид на комбинационни операционни схеми

ОКС1, ОКС2 от разгледания в точка 2.1.2 случай. Тези два участъка имат две общи

точки – входна и изходна. Всъщност, условната структура може да бъде

реализирана в смисъла на разглеждания тук случай по два начина, различаващи се

единствено по разбирането ни за функционирането на паралелните схеми. А то е

следното:

1. Входната точка има

функционалността демултиплексор, при което входните данни се подават само на

избраната паралелна схема, която получава истинния резултат. Алтернативната

схема функционира логически, но с неистинни входни данни (логически нули)

(фигура 2.1.11, средната схема). Тогава изходната точка има функционалността

мултиплексор, през който преминава резултатът, получен в избрания клон.

Функциите демултиплекиране и мултиплексиране са функции от входното условие,

означено Xj ;

2. Входната точка е

обща точка, при което паралелните схеми ОКС1, ОКС2 получават едни и същи общи

данни, функционират паралелно и всяка една от тях получава резултат (фигура

2.1.11, дясната схема). Изходната точка има функционалността мултиплексор, с

аргумент входното условие Xj, чрез който се избира и извежда на

изход истинният резултат.

Фиг. 2.1.11. Апаратна реализация на възможно развитие

след условие

Разклонената алгоритмична

структура може да бъде усложнена произволно, ако съдържа допълнителни условия.

Генерално обаче, като цялостна структура, тя има задължително една обща входна

точка и една или повече общи изходни точки. Във вътрешността си тя може да

съдържа отделни разклонени подструктури без ограничения на техния брой. Във

всички тези случаи обаче, при постигане на поставената цел, е възможно да бъде

приложено решението, илюстрирано на фигура 2.1.11, ето защо представеното

решение приемаме за общо.

Циклическа алгоритмична структура

Анализът на изчислителния

процес в много случаи изявява повторения на група действия. Обикновено това са

функционалности от вида

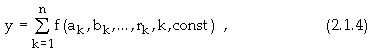

където с

a, b, … ,r са означени

итерационно променящи се променливи с известни начални стойности. Освен

адитивна, функционалността може да бъде и друга, например

мултипликативна.

Този факт обикновено ни

довежда до идеята за краткото му алгоритмично представяне чрез организиране на

общо изразените повторения с помощта на условие, което се нарича “условие за

край на повторенията” (УКП). Изказаното условие се формулира според характера

на повторенията, за които можем да кажем, че техният брой е предварително

известен или предварително неизвестен. Поради особената употреба на условния

преход в такива случаи, алгоритмичният синтез ни води до самостоятелната и

известна структура, наричана цикъл. Общо изразените повторения, аналогично на

математическата изразност (2.1.4), съставят тялото на цикъла.

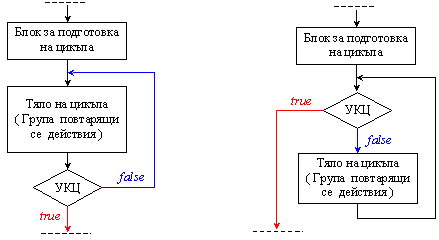

Известни са два вида

циклически алгоритмични структури:

1.

С предварително известен брой повторения ;

2.

С предварително неизвестен брой повторения.

За формалното

организиране на структури от първия вид се използва фактът, че техният брой е

предварително известен и той се контролира (или изразява) от отделна променлива

– брояч. Условието за край на повторенията, т.е. за край на цикъла (УКЦ) по

същество се изразява като въпрос относно съдържанието на този брояч. Общият вид

на циклическата алгоритмична структура е показан на фигура 2.1.12 в два

варианта – със следусловие и с предусловие.

Фиг. 2.1.12. Циклическа алгоритмична структура

Традиционното управление на

операционната част в едно изчислително устройство, което изпълнява циклическо

повторение на група микрооперации, изисква апаратна реализация на броячната

променлива. Оповестяващият сигнал на условието за край на цикъла се формира

чрез дешифратор, който се свързва към изходите на хардуерния брояч. От апаратна

гледна точка най-удобно е да се реализира декрементен брояч, при което

условието за край на повторенията настъпва, когато броячът се нулира.

Съдържанието нула се дешифрира лесно, то е универсално, не зависи от началната

стойност в брояча нито от стъпката за модификацията му. Ние ще изразяваме

по-нататък този признак чрез идентификатора EQ, чиито стойности кодират следния смисъл

![]()

В горното определение броячът е

означен с името Бр, а неговото съдържание - чрез ограждане на името му със

скоби (Бр).

Флагът EQ е един от

оповестяващите сигнали (фигура 2.1.1). Неговата стойност се доставя в

управляващия автомат, където се анализира. В резултат на това автоматът повтаря

превключването си в групата вътрешни състояния или излиза от този кръг.

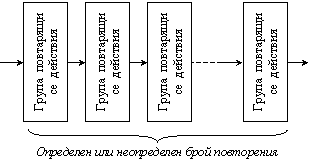

Алгоритмичната организация на

повторенията може да бъде постигната още и без формално условие, т.е. без

използване на условен алгоритмичен преход, чрез буквално и многократно

повторение на групата действия в тялото. Този подход за реализация се нарича

разгъване на цикъла и ще бъде разгледан допълнително в следващ раздел на тази

книга. При такава организация на повторенията (чрез буквалното им изписване) се

получава линейна алгоритмична структура, която вече разгледахме. Този подход се

практикува и на софтуерно ниво.

Задачата за премахване на

управлението (като част от управляващия автомат), която анализираме тук, в този

случай също може да бъде решена чрез пълно разгъване на цикъла, т.е. както вече

казахме по-горе – чрез буквална реализация на повторенията, показано на фигура

2.1.13. Това решение всъщност преобразува циклическата алгоритмична структура в

линейна. Основният извод, до който стигаме, е че и за тази алгоритмична

структура има без автоматна алтернатива. Разбира се за нея се “плаща” със

значително увеличаване на апаратните разходи.

Фиг. 2.1.13. Разгъване на цикъл чрез фактическо

повторение

За формалното организиране на

цикли от втория вид (с предварително неизвестен брой повторения) е необходимо

да се синтезира условие за край на повторенията. Това условие обикновено се

извлича (то е свързано с) от характера на обработваните данни. Най-често

условието е въпрос за постигaнe на отнапред зададена степен на точност или на

съответствие, т.е. то е проверка на отношение. Проверката на отношение в крайна

сметка се реализира чрез цифрово компариране. Организацията на този вид

повторения чрез пълно разгъване на цикъла, по начина показан на фигура 2.1.13,

е невъзможна.

След казаното за двата вида

цикли стигаме до заключението, че постигането на поставената тук цел за

разглежданата алгоритмична структура сме осъществили частично. Практическата

реализация на повторения чрез проверка на каквото и да било условие води до

операционна структура с обратна връзка. Изследването на безавтоматно управление

на операционни структури с обратни връзки се нуждае от специално внимание и ще

бъде изложено тук в следващите раздели.

2.1.3. Заключение

В заключение стигаме до извода,

че изразеният чрез алгоритмична схема изчислителен процес може да бъде

реализиран в изчислително устройство, чиято логическа структура не съответства

на декомпозицията на В. М. Глушков, т.е. не съответства на класическата

структура от фигура 2.1.3. В същност модифицираната операционна част, която

анализирахме, може да има вида на сложна комбинационна схема (еднотактова) или

многотактова във вид на конвейер, в случай, че в структурата бъдат използвани

фиксатори на междинни резултати.

От методична гледна точка,

представените тук разбирания за синтез на операционното устройство, се базират

на синтезирания за неговото функциониране алгоритъм. Този алгоритъм следва да

се детайлизира до степен, изявяваща описаните по-горе първични алгоритмични

структури, за които да бъдат приложени получените решения. Всички алтернативни

решения, които бяха посочени за основните алгоритмични структури, могат да

бъдат асоциирани с конвейерната организация на управлението. Така, като цяло,

крайната структура на операционното устройство ще представлява своеобразна

конкатенация на отделните решения. Управляващата част на това устройство се

“размива” по начини, които предстои да представим по-нататък. В резултат

устройствата с конвейерна организация придобиват нови характеристики, които са

обект на нашето изследване.

Предложеният подход предоставя

възможността за рязко намаляване на последователните тактове при изпълнение на

алгоритъма, включително до еднотактно, от една страна. В същото време, от друга

страна, допълнителното повишаване на производителността може да бъде

реализирано при конвейерна организация на обработката на последователна серия

от данни. Балансирането между тези две възможности е едно от

предизвикателствата пред Конструктора.

Като основен недостатък на

предложения подход бихме могли да посочим възможността за увеличаване на обема

на апаратните разходи в сравнение с чисто класическото конструиране на

изчислителното устройство.

2.2. Синхронни многотактови микроконвейерни звена

В този раздел е изложен метод за

апаратна реализация на циклически изчисления от вида с предварително известен

брой на повторенията. Последните

бяха анализирани в предходния раздел (фигура 2.1.12), където беше обоснована и

възможността за тяхната алтернативна реализация. Циклическата алгоритмична

структура е актуална по причина на необходимостта от честото й използване.

Цикли от различен вид се съдържат във всеки реален алгоритъм.

Тук е

представен синтезът на синхронни логически структури на устройства, които

определяме като многотактови микроконвейерни звена. Такова звено определяме

като многотактово, тъй като през логическите възли, от които то се състои,

многократно преминават междинните резултати на циклическото изчисление.

Синтезът на логическата структура се основава на синхронния метод за

управление, тъй като той е предпоставка за простота на управляващите схеми.

Циклическото тяло е определено като еднотактово, което може да се осигури по

начина, описан в предходния раздел.

2.2.1. Микроконвейерно

звено за цикъл с известен брой повторения

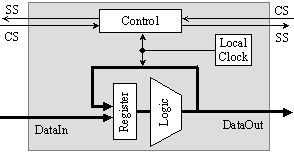

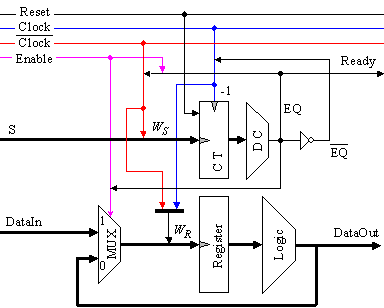

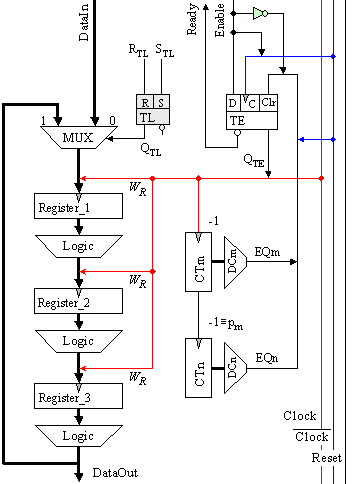

Многотактовото

микроконвейерно звено, което е синтезирано в съответствие с горе изказаните

съображения, съдържа вътрешна обратна връзка и може да се представи чрез

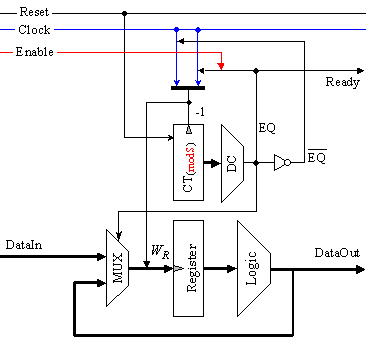

обобщената логическа структура от фигура 2.2.1.

Фиг. 2.2.1. Обобщена структура на многотактово МКЗ

Структурата съдържа три

основни елемента – конвейерен регистър фиксатор (Register) и съвкупност

от комбинационни логически схеми (Logic), реализиращи необходимата

преработка на данните. Най-съществената особеност на тази част от структурата е

вътрешната обратна връзка, която е естествена предпоставка за състезания в

превключванията. По тази причина регистърът в звеното следва да се реализира

чрез динамични тригери със структура Edge, превключващи се само по един

от фронтовете на управляващия сигнал за запис. Обратната връзка е тази, която

фактически реализира възможността за циклическото повторение на операциите,

които се изпълняват от комбинационната схема. Тя пренася междинните резултати

от изхода на звеното обратно към входа на регистъра.

Третият елемент (Control)

обединява всички елементи, реализиращи вътрешно-схемното управление на

структурата. Този елемент е неразделна част от схемата на звеното и се получава

в процеса на неговия синтез. Освен това той има задачата да създаде

предпоставки за диалог със съседните микроконвейерни звена, като обработва и

генерира съответните управляващи сигнали CS и флагове на състоянието SS, в което може да

се окаже звеното. Двигател на превключванията в схемата е локалният тактов

генератор, което означава, че тя е синхронна и независима от останалите

елементи на конвейера, в който може да бъде вградена.

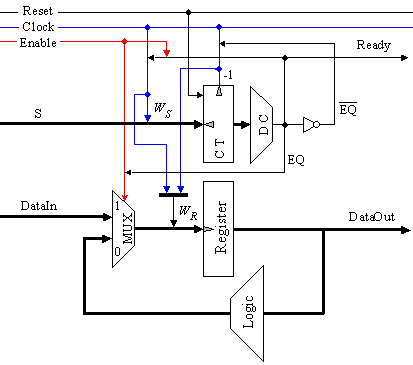

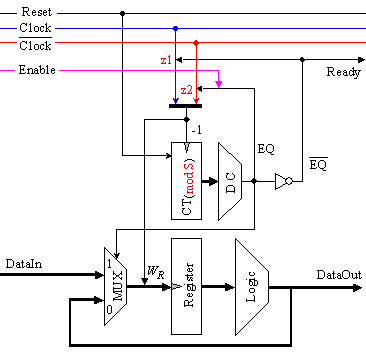

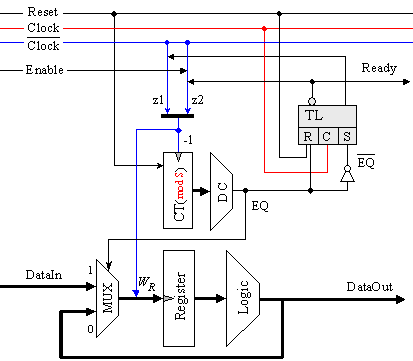

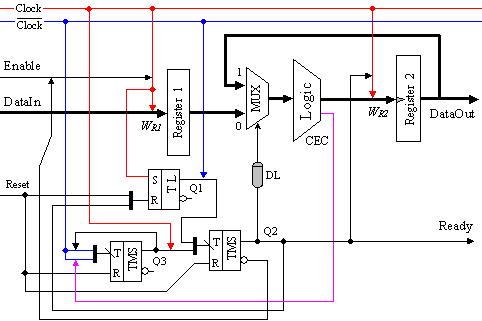

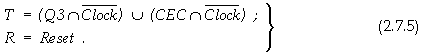

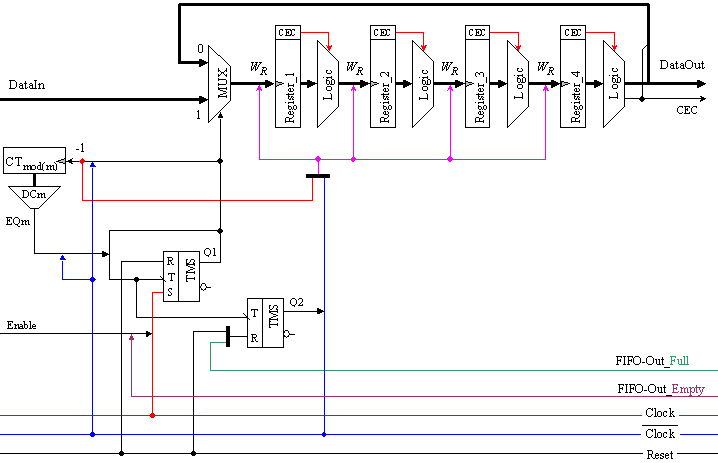

Синтезираната логическа структура на синхронно конвейерно звено, което

изпълнява цикъл от вида с отнапред известен брой повторения, с еднотактово

операционно тяло, е представена на фигура 2.2.2.

Тъй като по условие разглеждаме цикъл с известен брой повторения,

апаратната реализацията на условието за край на цикъла изисква използването на

двоичен брояч по модул S. Синтезът на такъв брояч СТ(modS) се осъществява чрез

методиката за синтез на крайни автомати. В представената реализация е прието

началната стойност в брояча да бъде нула, която се постига чрез сигнал Reset.

Сигналът Reset установява принудително в изходно състояние логическата

структура. По този начин, когато броячът отброи S на брой входни импулси (-1),

ще се окаже отново в изходно (нулево) състояние, което е удобно за следващи

изпълнения.

Синтезираната за

декрементните импулси (-1) логическа функция има следния вид

![]()

В структурата има

конвейерен регистър фиксатор Register за временно съхранение на данните,

операционна комбинационна схема Logic, реализираща някаква обща линейна

алгоритмична структура. Същата, както отбелязахме в началото, може да бъде

постигната чрез обединяване на операциите и прилагане на методите за проста

разделителна или неразделителна функционална декомпозиция на логическите

функции. Тези методи могат да осигурят за операционната логика минимална

логическа форма, както и минимално време за превключване.

Фиг. 2.2.2. Многотактово микроконвейерно звено с

брояч по модул S

Към данновия вход на

регистъра фиксатор е включен мултиплексор MUX, за реализация на входната точка

в циклическата структура. Операционната част, обхваната от обратната даннова

връзка, се превключва толкова пъти, колкото тактови импулса постъпят в брояча.

В тази структура броячът се превключва по задния фронт на входните импулси, а

регистърът записва данни по предния фронт на управляващия импулс W.

Дешифраторът DC, включен

към изходите на брояча разпознава нулевото му съдържание, като формира

стойността на сигнал EQ.

Чрез този сигнал и останалите входни за структурата сигнали – Reset, Enable

и Clock, се реализира цялостното управление на устройството. В изходно

състояние съдържанието на регистъра и брояча е нула. Това означава, че флагът EQ

е вдигнат, EQ=1. Тази стойност на флага не допуска тактовите импулси до

схемата. В същото време той се използва като изходен сигнал, който оповестява

състояние на готовност Ready=1. Състоянието на микроконвейерното звено е

фактор при управлението на следващото микроконвейерно звено.

Управлението на логическата

структура се изразява в това, че постига отделяне в необходимия момент на S на

брой последователни тактови импулси, изрязани от безкрайната последователност Clock

и подадени на входа на брояча. Първият от тези импулси, който се създава в

схемата в отговор на асинхронния входен сигнал Enable, зарежда началните

(входните) данни във регистъра фиксатор и превключва брояча в състояние (S-1).

В резултат на това изчезва сигналът EQ (EQ=0), Тази нова стойност

на сигнала превключва мултиплексорът MUX към обратната връзка. Така, в това

състояние, се реализират S последователни превъртания на данните DataOut през

операционната комбинационна схема Logic. След възникване на условието за

край на цикъла (EQ=1), микроконвейерното звено декларира своята

готовност Ready на следващите, блокира постъпването на нови тактови

импулси Clock и отваря входната даннова шина DataIn, като превключва

мултиплексора MUX от обратната връзка отново към входната шина.

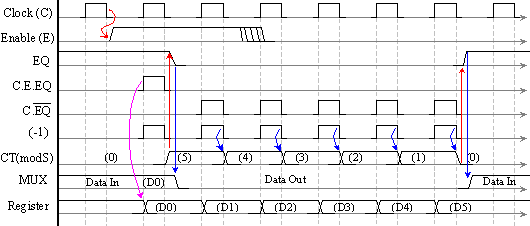

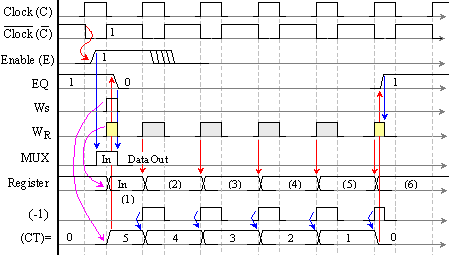

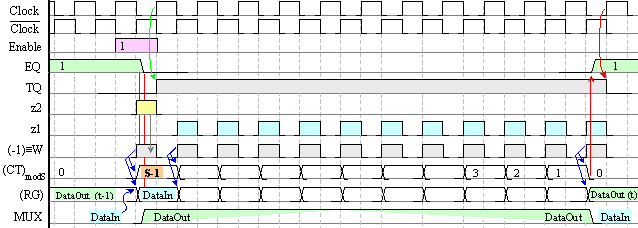

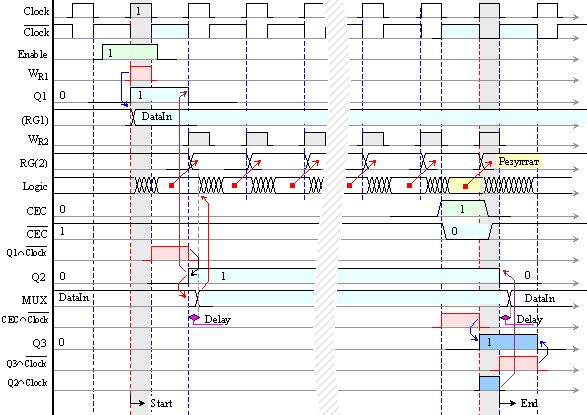

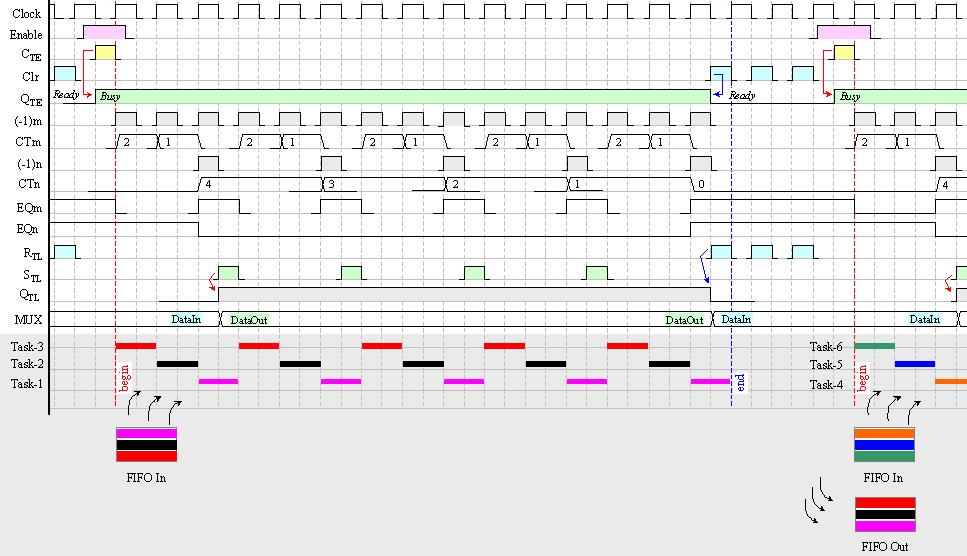

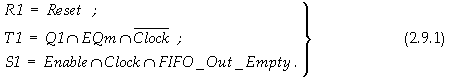

Описаният изчислителен

процес се постига апаратно и без външно микропрограмно управление. Единственият

двигател на превключванията след стартовия сигнал Enable, е тактовият

генератор. Този процес е илюстриран с времедиаграмата от фигура 2.2.4.

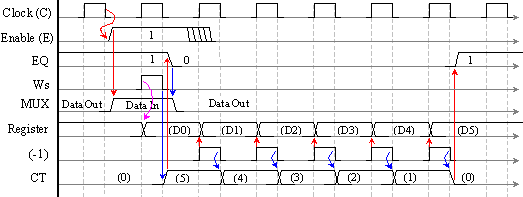

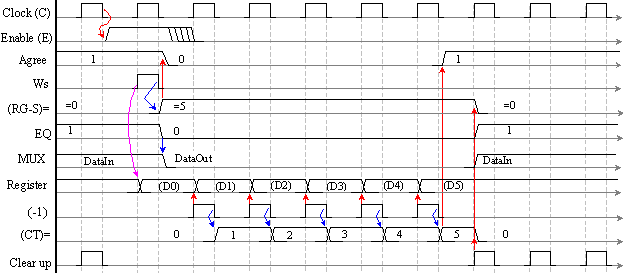

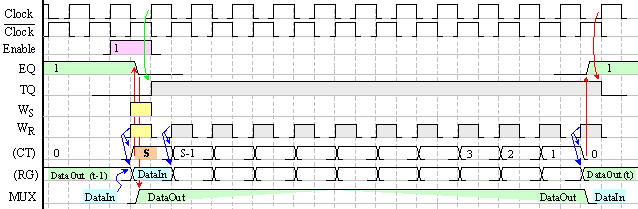

Примерната времедиаграма по-долу на фигура 2.2.3 изразява цикъл с 6 повторения.

След излизане от цикъла на изход излиза резултатът D6=f(D5).

Фиг. 2.2.3. Времедиаграма за изпълнение на цикъл

Структурата на циклическата

организация функционира правилно само ако сигналът Enable от предходната

секция се появява след задния фронт на тактовия импулс, както е показано на

времедиаграмата.

Изходният за

микроконвейерното звено сигнал Ready, който е еквивалентен на сигнала EQ,

се генерира след задния фронт на тактовия импулс, който нулира съдържанието на

контролния брояч. Това го прави използваем в качеството му на сигнал Enable

към следващата секция. При това условие той удовлетворява и изказаното по-горе

условие.

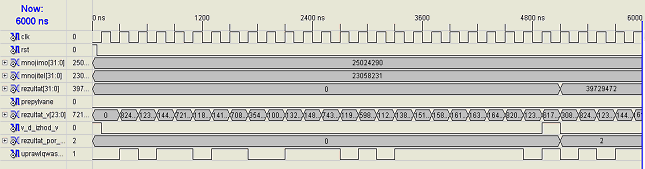

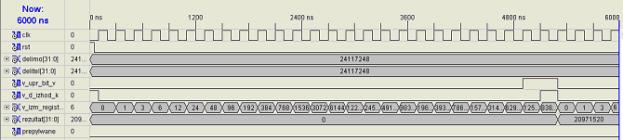

Практическото

експериментиране на така синтезираното управление на циклическата структура е

извършено върху интегрална схема Spartan II на фирма Xilinx.

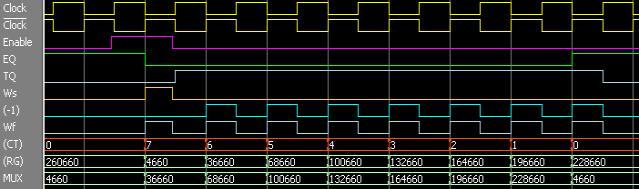

Времедиаграмата на модела, която е представена на фигура 2.2.4 (по-долу)

напълно потвърждава казаното за структурата от фигура 2.2.2.

Както се вижда, моделът е изпълнил

цикъл с 8 повторения. За по-лесна проверка в операционната комбинационна схема Logic,

е заложено итерационното изчисление на натрупващата се сума Sk

= Sk-1

+ 32000 ,

при S0=4660 .

Фиг. 2.2.4. Времедиаграма на модела

Така, върху последната

абсциса Fixed Data от времедиаграмата на модела, се виждат

последователно получаваните числени резултати:

4660, 36660, 68660 и т.н.

Следва да отбележим, че

цикълът от вида с предусловие за тази алгоритмична структура е безсмислен. Това

се дължи на факта, че броят на повторенията е предварително известен и

задължителен, а така също не е и нулев.

2.2.2. Микроконвейерно звено за цикъл с

променлив брой повторения

Има случаи, когато цикълът

е от вида с известен брой повторения, но този брой като стойност е променлив и

зависи от предходни изчисления или от някакви условия. В този случай не е

възможно контролният брояч в структурата на звеното да работи винаги по един и

същи модул на броене. Неговото начално съдържание трябва да бъде зареждано в

конвейерното звено заедно с останалите входни данни, подлежащи на преработка.

Следователно необходимо е да се използва универсален двоичен брояч. Неговото

начално съдържание може да бъде различно, от където следва, че най-удобно за

реализацията ще бъде ако този брояч бъде декрементен. Условието за край на

цикъла ще се формира от дешифратора DC по същия начин, като разпознава

съдържание нула и формира сигнала EQ.

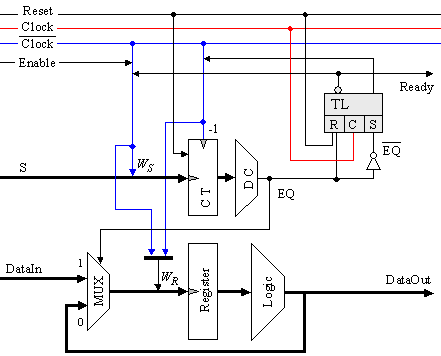

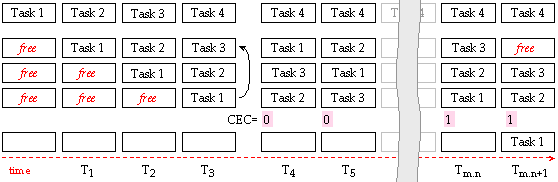

На фигура 2.2.5 е представена логическата структура

на звено, която е синтезирана при изказаните по-горе условия.

Логическата структура на

конвейерното звено има още един даннов вход, по който се зарежда началното

съдържание S на брояча СТ. Това се осъществява по задния фронт на импулса WS, който има следната логика

![]()

Записът на входните данни

се осъществява малко по-рано във времето, по предния фронт на импулса WR. Логиката на този сигнал е следната

![]()

където декрементните импулси (-1) имат

логиката

![]()

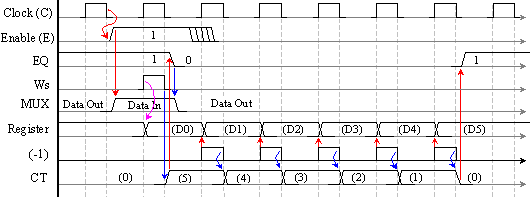

На фигура 2.2.6 е

представена времедиаграмата за изпълнение на цикъл от 6 повторения. В същност

броят на превъртанията е 5, но последната итерация D6=f(D5) се

изпълнява от операционната схема върху съдържанието на регистъра фиксатор,

което е D5. Върху изходната шина обаче се намира резултатът D6.

Фиг. 2.2.5. Многотактово (програмируемо) конвейерно

звено

с отнапред известен, но променлив брой на повторенията

Както може да се види, импулсът за

запис на нови данни и старт на изчисленията в структурата се дава от сигнала Ws

. Използването на сигнала EQ в разглежданата структура е аналогично на

изложеното за предидущата. За тази алгоритмична

структура цикълът с предусловие също е безсмислен. По принцип обаче е възможно

такава ситуация на бъде създадена. Това може да се случи, когато внесената в

брояча начална стойност е S=0. Тази начална стойност не предполага никаква

преработка на входните данни, но понеже операционната схема Logic е

включена към изхода на регистъра фиксатор, тя задължително ще изпълни своето

изчисление, което в този случай ще бъде грешка. Ако възможността за

неизпълнение на действията от тялото на цикъла е реална, тогава се налага

операционната схема Logic да бъде преместена в обратната връзка (фигура

2.2.5). Така записаните във фиксатора входни данни ще излязат без обработка на

изход. Логическата структура има вида, представен на фигура 2.2.7.

Фиг. 2.2.6. Времедиаграма за изпълнение на цикъл с 6

повторения

Фиг. 2.2.7. Микроконвейерно звено за цикъл с

предусловие

Положението на

операционната схема в структурата е такова, че изчисленият от нея резултат,

като функция от текущото съдържание на регистъра фиксатор, се записва в него

при следващия тактов импулс. Така, ако в брояча бъде заредено числото S=5,

както в случая по-горе, необходимият резултат D6 ще остане на изхода на

комбинационната схема. В случая, след 5 такта в регистъра фиксатор ще се намира

5-тият по ред резултат D5 и той ще бъде подаден на изход по шината DataOut.

Това положение е изобразено на времедиаграмата от фигура 2.2.8.

Фиг. 2.2.8. Времедиаграма за изпълнение на цикъл с 6

повторения

За да бъде достъпен за

четене резултатът D6, е необходим още един тактов импулс, който да го запише в

регистъра. От тук следва, че началната стойност на брояча трябва да бъде

увеличена с единица и да бъде (S+1).

Представеният метод за

реализация на самоуправляващи се циклически структури е успешно приложена при

проектиране на реални изчислителни устройства. Проектът реализира конвейерни

устройства за умножение и деление на 32-битови числа (8+24)[b], представени във форма

с плаваща запетая и структура (P±M). По-долу на

фигури 2.2.9 и 2.2.10 са представени времедиаграми за функционирането на реално

проектираните устройства.

Фиг. 2.2.9. Времедиаграма на операция умножение

Фиг. 2.2.10. Времедиаграма на операция деление

Върху времедиаграмите може

да се види, че при умножение, отпечатъците, които предоставя програмната среда,

интерпретирайки съдържанието на регистрите като цяло число, съответно 250254290

и 23058231, представляват съмножителите X=1,98 и Y=1,33. Произведението

(отпечатък 39729472) е числото 2,6334.

При деление операндите са еднакви (24117248º1,75)

частното е 1 (20971520º1,0).

2.2.3. Заключение

От методична гледна точка, изложените тук решения могат да се разглеждат като метод за синтез на конвейерни звена. Цялостният синтез на конвейерното звено се основава на синтезирания алгоритъм за функциониране. Този алгоритъм се детайлизира според разбиранията, формулирани в предходния раздел 2.1, с цел да бъдат изявени описаните там първични алгоритмични структури, за които да бъдат приложени получените решения.

Основното достойнство на

предложения метод се състои във възможността за рязко намаляване на

последователните тактове при изпълнение на алгоритъма, включително до

еднотактно. Така, като цяло, при условията на поставената задача, апаратната

самоуправляваща се реализация на изчислителния процес води до максимална

производителност. Получената логическа структура представлява конвейерно звено

и като такова може да бъде включвано като елемент както на синхронни, така и на

асинхронни конвейери, възможност, която ще бъде показана и изследвана по-късно

тук.

Като основен недостатък може да се посочи

известното увеличаване обема на апаратните разходи в сравнение с чистите такива

за операционната част на автоматно управляваното устройство. Това, разбира се,

е “платената цена” за постигнатите положителни ефекти. Ще формулираме още

следните изводи:

1. Изразеният чрез

алгоритмична схема изчислителен процес (фигура 2.2.1) може да бъде реализиран в

изчислително устройство, чиято логическа структура не съответства на

декомпозицията на В. М. Глушков, т.е. не съдържа управляваща част и при това се

подчинява на общата ни представа за тази реализация;

2. По този начин,

изказаното тук в раздел 2.1 разбиране, относно възможността всички основни

видове алгоритмични структури да се реализират като самоуправляващи се апаратни

структури, се доказва и се потвърждава и за разгледаните тук случаи;

3. Алгоритмичната

структура цикъл все още не е напълно изследвана, тъй като за нея съществуват

още няколко разновидности, като например цикли с предварително неизвестен брой

повторения;

4. В същност,

операционна част на предлаганата тук структурата може да има вида на сложна

комбинационна схема (еднотактна) или да има вида на конвейер, ако в структурата

бъдат използвани междинни фиксатори, случай, който ще бъде разгледан тук

по-късно;

5. Предложеният метод

е успешно използван при изследване на реални устройства за умножение и деление

на 32-битови числа с плаваща запетая по стандарта с изместен порядък.

2.3. Синхронни многотактови микроконвейерни

звена, тактувани с един и същи фронт

Основната концепция, за редукция на

управляващите крайни автомати (като съставна част от всяко цифрово устройство),

която ние продължаваме и тук да прилагаме, беше обсъдена детайлно в предходните

раздели. Постигането на устройства, които съответстват на тази концепция е

възможно, но поради своето многообразие последните продължават да бъдат обект

на изследване и в настоящия раздел. Тук се разглежда постановката на задачата

от предходния раздел, но при условие, че всички логически възли, изграждащи

логическата структура на циклическото микроконвейерно звено, се превключват

единствено по предния фронт на управляващите ги импулси. Това изследване се

налага да бъде извършено, тъй като в реални условия предлаганите градивни

елементи, не винаги осигуряват разнообразието, което беше използвано в

предходните решения. Реалните условия се характеризират с това, че проектантът

не винаги има на разположение градивните елементи, които биха му осигурили

оптималната реализация. В такива случаи му се налага да съобразява проекта с реалните

наличности. Синтезът на логическите структури, които са представени по-долу, е

извършен при условието, че логическите възли ще използват само преден фронт на

управляващите импулси.

Предложените вече решения

за циклически алгоритмични структури от вида с предварително известен брой

повторения използват в своите схеми декрементни броячи, които се превключват по

задния фронт на входните импулси (-1). Тъй като в много синхронни елементи, а

така също и в програмируемите логически клетки на CPLD и FPGA, градивните

елементи реализират превключвания единствено по предния фронт на управляващите

импулси, тук са предложени съответните алтернативни решения. Това са логически

структури, в които всички логически възли се превключват по преден фронт.

Въпросът е актуален с това,

че при използване на еднофазов тактов генератор за синхронизация на

превключванията в логическите структури, маркирането на отделни фиксирани

моменти в рамките на тактовия период е затруднено, а то е крайно необходимо в

смисъла на нашата концепция за управление. Тук се има предвид това, че в

самоуправляващите се структури се налага да се изграждат различни обратни

връзки, които създават условия за възникване на състезаващи се събития, т.е. на

състезаващи се превключвания. Последните не винаги е възможно да бъдат

овладени, така че синхронизацията изисква приложение на различни подходи,

включващи използването на противосъстезателни елементи, на комбинирано

използване на схеми, превключващи се по различни фронтове, както и на

използване на няколко-фазов тактов генератор. Въпреки че структурите са

синхронни, реалните закъснения ни задължават да отчитаме асинхронността на

събитията.

2.3.1. Микроконвейерно

звено за цикъл с известен брой повторения

Като решение на изявения

проблем със синхронизацията и на възможното многообразие тук са представени

синтезираните логически структури и техните изследвания в два варианта, които

съответства на условията от предходния раздел. Става дума за цикли с

конструктивно предопределен брой повторения и за цикли с известен, но променлив

брой на повторенията. На фигура 2.3.1 е представена логическа структура на

микроконвейерно звено от първата разновидност.

Структурата изпълнява

действията в тялото на цикъл чрез апаратната им реализация в комбинационната

схема Logic. Входните данни за всяка поредна итерация се поддържат от

регистъра фиксатор, който записва новите данни по предния фронт на

управляващите импулси WR. Условието за край

на цикъла EQ се формира от дешифратора DC. В изходно състояние

съдържанието на брояча CT(modS) е нула, при което EQ=1

и входният даннов мултиплексор MUX е включен към шината DataIn. Въпреки

че структурата се тактува непрекъснато, в нея не се извършват превключвания.

Изчисленията

започват с появата на разрешаващия сигнал Enable, както е показано чрез

времедиаграмата на фигура 2.3.2. За правилно функциониране сигналът Enable

следва да се появява по предния фронт на тактовите импулси и да има

продължителност не повече от един период.

И в тази структура

последният резултат D6 се получава от съдържанието на регистъра фиксатор, което

е равно на D5, т.е. D6=f(D5). При това циклическите превъртания са 5, т.е. в

общия случай (S-1).

Фиг. 2.3.1. Многотактово микроконвейерно звено, с

брояч по модул S,

работещo по преден фронт

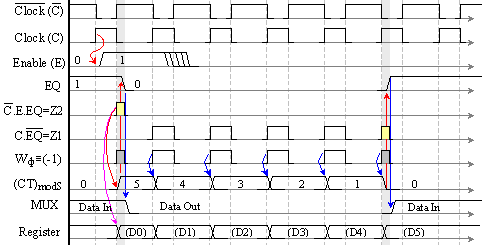

Както се вижда от

примерната времедиаграма, за надеждна синхронизация на превключванията е

използван и инверсният тактов сигнал not(Clock). В изразения процес на превключване има два особени момента,

които следва да бъдат пояснени.

Фиг. 2.3.2. Времедиаграма за изпълнение на цикъл от 6

повторения

Първият се отнася до

скъсената продължителност на първия и последния декрементни импулси (вижте

абсцисата на сигнал (-1)). Логиката на импулсите (-1) има следния вид

![]()

В структурата от фигура

2.3.1 броячът СТ се превключва по предния фронт на входните декрементни импулси

(-1) и новата стойност на сигнала EQ възниква с голямо закъснение върху

изхода на дешифратора DC. Закъснението е сума от времето за превключване на

брояча плюс времето за превключване на дешифратора. Едва след това, като

следствие, разпространяващият се по обратната връзка сигнал EQ

(респективно и неговата инверсна стойност), затваря чрез нулевата си стойност

със закъснение съответната конюнкция (вижте точка z1 и точка z2).

В резултат на това

закъснение, продължителността на тези скъсени импулси, е равна на времето за

превключване на брояча, плюс времето за превключване на дешифратора, плюс

времето за превключване на останалите логически елементи в обратната връзка.

Може да се твърди, че това време е напълно достатъчно за правилното

превключване на брояча, дешифратора и елементите в обратната връзка. И въпреки

че обратната връзка поражда това състезание, то не се самовъзпроизвежда,

благодарение на използваните в брояча противосъстезателни тригери със структура

Edge.

Вторият особен момент се отнася

до продължителността на инверсната фаза на тактовия сигнал. Тъй като тя

определя престоя на началните входни данни в регистъра фиксатор (вижте

абсцисата на фиксатора), то времето за първото операционно изчисление в схемата

Logic ще бъде по-малко от продължителността на периода на тактовата

последователност. От тук следва, че за получаване на правилни резултати, трябва

да се предяви изискване както към тактовата честота, така и към коефициента на

запълване на тактовия сигнал, който следва да е възможно най-малък. За всяко

следващо изчисление (циклическо повторение), освен за първото, ще бъде отделено

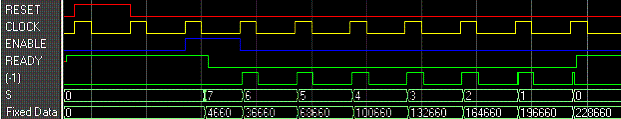

време, равно на продължителността на цял период.

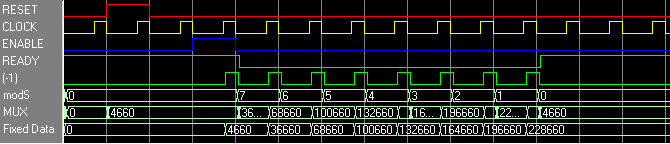

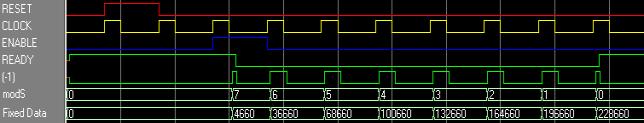

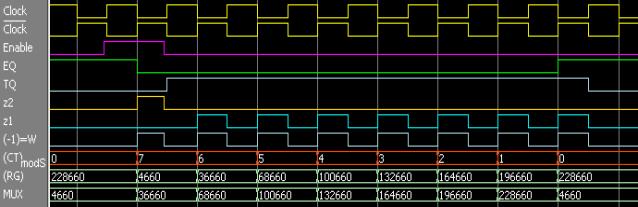

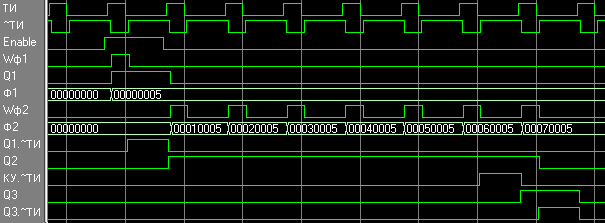

Практическата проверка на

синтезираната структура е изпълнена в средата ISE 10.1 на фирма Xilinx

за интегрални схеми от серията Spartan 3E. На фигура 2.3.3 е представена

работата на генерирания модел. Изпълнен е цикъл с 8 повторения. За по-лесна

проверка в операционната комбинационна схема Logic е заложено

итерационното изчисление на натрупваща се сума: Sk=Sk-1+32000 , при

S0=4660. Така върху последната абсциса Fixed

Data от фигура 2.3.3 се виждат получаваните числени резултати: 4660, 36660,

68660 и т.н.

Фиг. 2.3.3. Времедиаграма на Xilinx-модела

2.3.2. Микроконвейерно звено за цикъл с

променлив брой на повторения

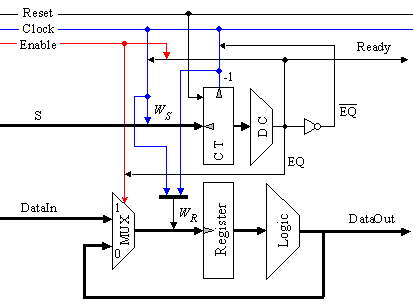

На фигура 2.3.4 е представена

синтезираната логическа структура, съответстваща на циклическа алгоритмична

структура от вида с предварително известен брой повторения, който обаче е

променлив и е функция на предходни етапи на изчислителния процес.

Циклическата организация с

променлив брой повторения изисква използването на декрементен програмируем

двоичен брояч, в който определената стойност S се записва в качеството си на

негова начална стойност. Максимално възможната стойност е ограничена от модула

за броене. Отчитайки споменатата програмируемост, логическата структура има

отделен вход към двоичния брояч CT. Освен това е осигурено всички нейни

логически възли с памет да се превключват по преден фронт на управляващите

импулси. Условието за край на цикъла се формира от дешифратора DC, който

разпознава съдържание нула и формира сигнала EQ. Управлението на

събитията, свързани с измененията на съдържанието на брояча, се постига чрез

логическите схеми в неговите обратни връзки.

Фиг. 2.3.4. Програмируемo микроконвейерно звено,

работещo по преден фронт

В изходно състояние

съдържанието на брояча CT е нула (СТ)=0, поради което стойността на сигнала EQ е EQ=1. По този

начин входният мултиплексор MUX е включен към шината DataIn. Въпреки че

в това състояние структурата се тактува неперекъснато, в нея не се извършват

превключвания.

Изчисленията започват с

появата на разрешаващия сигнал Enable, както е показано на фигура 2.3.5.

За правилно функциониране сигналът Enable следва да се появява по

предния фронт на тактовите импулси и да има продължителност не повече от един

период. Времедиаграмата представя изпълнение на цикъл от 6 повторения. Запис на

нови данни и старт на изчисленията в структурата, се дава от сигналите WS и WR, които се формират

според следната логика

![]()

![]()

Използването на сигнала EQ

в разглежданата структура е аналогично на изложеното за предидущата. За тази

структура цикълът с предусловие е възможен. В този случай, възможността за

неизпълнение на действията от тялото на цикъла налагат операционната схема Logic да бъде преместена в обратната връзка, а на изход DataOut

да излиза съдържанието на регистъра фиксатор. Така, ако записаната начална

стойност в брояча CT се окаже равна на нула (S=0), то записаните във фиксатора

входни данни ще излязат без обработка на изход.

Фиг. 2.3.5. Времедиаграма на структура, работеща по преден фронт

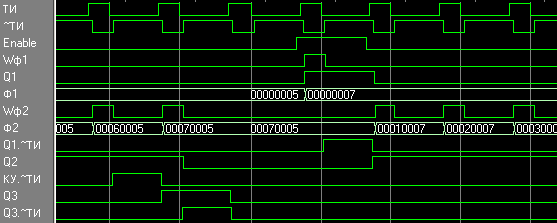

Практическата проверка на синтезираната

тук структура е изпълнена в средата ISE 10.1 на фирма Xilinx [XIL84], за интегрални схеми от

серията Spartan 3E. На фигура 2.3.6 по-долу е представена работата на

генерирания модел. Изпълнен е цикъл с 8 повторения при начална стойност S=7.

Както в предидущия модел, за по-лесна проверка, в операционната комбинационна

схема Logic е заложено аналогичното итерационно изчисление на

натрупващата се сума: Sk=Sk-1+32000, при S0=4660. Така

върху последната абсциса от фигура 2.3.6 се виждат получаваните числени

резултати.

Фиг. 2.3.6. Времедиаграма на Xilinx-модела

2.3.3. Заключение

Изследването показва, че

логическите структури с обратни връзки не губят работоспособност при синхронно

превключване на логическите възли само по един от фронтовете на тактовите

импулси, но създават условия за реални състезания. В началото и в края на

работния цикъл тези състезания водят до стробиране на тактовите импулси. Освен

това се изявяват повишени изисквания, свързани с продължителността на началното

изчисление, които задължава проектанта да въвежда ограничение не само върху

тактовата честота, но и върху коефициента на запълване. Вътрешносхемните състезания

не винаги е възможно да бъдат овладени, така че синхронизацията изисква

приложение на различни подходи, включващи използването на противосъстезателни

градивни елементи, на комбинирано използване на схеми, превключващи се по

различни фронтове, както и на използване на няколко фазов тактов генератор.

Въпреки че структурите, които тук са проектирани като синхронни, реалните

закъснения ни задължават да отчитаме асинхронността на събитията.

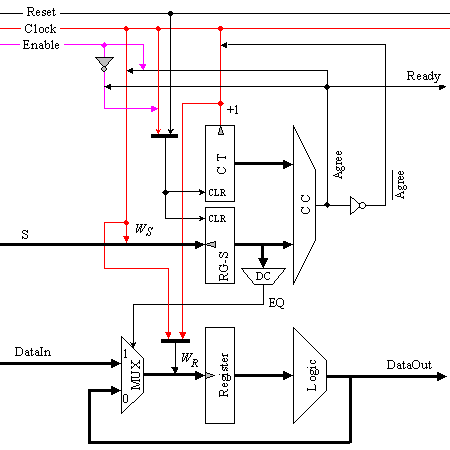

2.4. Програмируемо многотактово микроконвейерно

звено с цифров компаратор

Синтезираните в

предходния раздел конвейерни звена, за които бяха използвани логически възли,

работещи по един и същи фронт, притежават параметри, които не винаги биха могли

да бъдат удовлетворени. Става дума за стробирането на управляващите импулси в

началото и в края на изчислението. Въпреки че работоспособността на тези звена

беше доказана, този факт буди известни опасения. Сам по себе си той за сетен

път доказва, че синтезът на логически структури, дори при синхронен метод за

управление, изисква възможности за ясно фиксиране на повече от един момент в

рамките на един тактов период. При тактуване с еднофазов тактов генератор това

е постижимо единствено чрез подходящо комбиниране на логически възли, работещи

по различни фронтове. Ето защо тук в този раздел отново използваме тази възможност,

като представяме програмируемо микроконвейерно звено за изпълнение на цикли с

известен брой повторения. Синтезираната логическа структура, която за разлика

от всички предидущи, използва инкрементен брояч. Структурата на

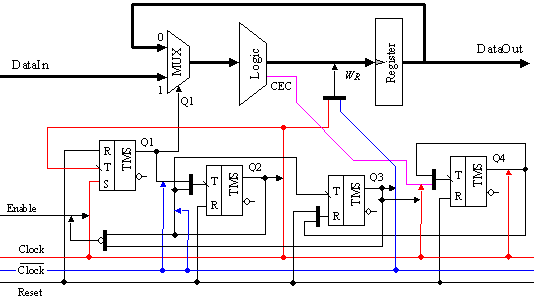

микроконвейерното звено е показана на фигура 2.4.1.

Фиг. 2.4.1. Програмируемо микроконвейерно звено с

компаратор

Структурата

на звеното съдържа инкрементен по заден фронт брояч СТ, контролен регистър

RG-S, който съхранява общия брой повторения. Този регистър записва данни също

по заден фронт. Регистърът фиксатор Register обаче записва данни по преден фронт.

В

изходно състояние съдържанието на брояча СТ, както и това на регистъра на

контролната стойност RG-S, е винаги нула, което се постига чрез импулсите,

постъпващи на входовете CLR (Clear up). След стартиране на изчислителния

процес от сигнал Enable, входните данни се записват в регистъра фиксатор

по входната даннова шина DataIn, контролната стойност S се записва в

регистър RG-S, а съдържанието на брояча започва да расте. Последното

непрекъснато се сравнява с контролната стойност S с помощта на схемата за

сравнение СС, която генерира в края на процеса сигнала за съвпадение Agree, т.е. Agree=1, когато (CT)=(RG-S).

Изчислителният процес

протича под управлението вътрешни и външни сигнали, чиято логика е следната

![]()

![]()

![]()

![]()

Надеждността на превключванията и премахването на състезанията в

структурата са осигурени чрез логически възли с различно превключване.

Регистърът RG-S и броячът СТ се превключват по заден фронт, а регистърът

фиксатор – по преден. Процесът на функциониране на проектираната логическа структура е

представен чрез времедиаграмата от фигура 2.4.2.

Фиг. 2.4.2. Времедиаграма за изпълнение на цикъл с 6

повторения

От сравнението на всички резултати,

представени в предходните раздели и получените тук, отнасящи се до циклическите структури, се налага следния извод:

структури, използващи логически възли, които се превключват по един и същи

фронт на управляващите импулси, са склонни да генерират вътрешни за себе си

състезания. Това води до стробиране на управляващите импулси в началото и в

края на изчислителния процес, т.е. до намаляване на тяхната продължителност в

сравнение с продължителността, която тези същите импулси имат в междинните

тактове на процеса. В същото време, структурите, които комбинират различни

превключващи фронтове, не генерират състезания във вътрешността си. Възможните

за някои структури състезания обаче не се самовъзпроизвеждат благодарение на

използваните противосъстезателни тригерни елементи. В този смисъл за такива

структури можем да говорим, че притежават частична асинхронност. Представените до

момента резултати доказват възприетата в началото концепция относно

възможността за апаратна реализация на структури, свободни от автоматно

управление.

2.5. Микроконвейерно звено за цикъл с неизвестен

брой повторения

В

този раздел отново разглеждаме циклическа алгоритмична структура, но този път

тя е от вида с предварително неизвестен брой повторения.

Този вид алгоритмична структура се

характеризира с това, че условието за край на цикъла се формулира въз основа на

определено числено отношение. Логиката на това отношение се проверява

многократно върху стойности на променливи, които се преизчисляват итерационно в

тялото на цикъла. Споменатото отношение се формулира в общия случай при синтеза

на алгоритъма и се основава върху ограниченията на изходните числени данни за задачата,

т.е. то е отнапред известно и обикновено има следния вид

![]()

където с ![]() е означено поредното

(k-то) изменение на

стойността на контролната променлива Var, а с e е означена стойността на отнапред зададената степен на точност.

Степента на точност изразява минимално приемливата за изчисляваните резултати

грешка.

е означено поредното

(k-то) изменение на

стойността на контролната променлива Var, а с e е означена стойността на отнапред зададената степен на точност.

Степента на точност изразява минимално приемливата за изчисляваните резултати

грешка.

По причина на това, че

изчисленията, свързани със стойността на кода на условието за край на цикъла

(2.5.1), определят техния ход, те следва да се реализират

в конвейерното звено. Като имаме предвид възможно най-елементарния случай,

когато изчислението в тялото на цикъла е еднотактно, излиза че то изцяло ще се

реализира от операционната комбинационна схема, която неизбежно ще присъства в

структурата на звеното. Още веднъж подчертаваме, че имаме предвид циклическо

тяло с линейна алгоритмична структура, която може да се сведе до линейна

конвейерна или в крайна сметка до еднотактна комбинационна схема, по начина

показан в първия раздел.

2.5.1. Логическа структура

на звеното

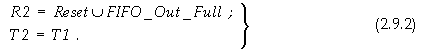

Апаратната реализация на

това изчисление, като синхронна или като асинхронна структура, е принципно

еднаква. В представения по-долу вариант (фигура 2.5.1) синтезираната логическа

структура е синхронна и се тактува от еднофазов тактов генератор. Тя съдържа

последователно включени мултиплексор MUX, операционна комбинационна схема Logic,

която реализира изчисленията в тялото на цикъла, включително и изчислението на

стойността на кода на условието за край на цикъла, означено CEC (Condition

End of Cycle). Фиксаторът е регистър, изграден от противосъстезателни

тригери със структура Edge, превключващи се по преден фронт. Обратната

даннова връзка осигурява циклическото изчисление. Логическата структура се

управлява от логическа схема, образувана от четири Т-тригера T1, T2, T3 и T4

със структура Master-Slave, чиито изходи са означени Q1, Q2, Q3 и

Q4, и които се превключват по заден фронт.

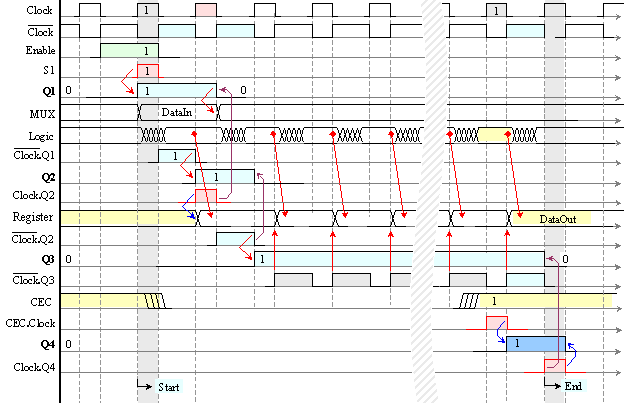

Фиг. 2.5.1. Циклическо звено с неизвестен брой на

повторенията

Циклическият алгоритъм е

реализиран изцяло апаратно. Процесът на функциониране на структурата, който е

представен на фигура 2.5.2, изяснява функцията на управляващата схема.

Синтезът на последната е

постигнат по време на синтеза на цялостната структура на конвейерното звено. С

други думи синтезът на управляващата схема не може да бъде отделен, както

методиката за синтез на крайни автомати е отделена от синтеза на операционната

част, положение, което беше обосновано в първи раздел. Управляващата схема на

звеното е следствие от организираните в неговата структура превключвания.

Единственият “двигател” на получената логическа структура е тактовият сигнал Clock.

Липсата на управляващ краен автомат я превръща в конвейерно звено, изключително

удобно за вграждане в конвейерно организирани апаратни изчислителни структури.

Структурата се предлага като метод за реализация на микроконвейерни

многотактови звена, който е в съответствие с основната концепция на

изследването.

Логическата структура на

звеното може да се намира в две състояния – изходно и работно. В изходно

състояние обратната връзка се поддържа включена от мултиплексора MUX, тъй като

изходът на тригер Т1 е установен в състояние нула Q1=0. В регистъра фиксатор се

съдържат получените при предпоследното изчисление резултати, които са достъпни

за четене. В това състояние структурата е подложена на непрекъснато тактуване,

но в нея не се извършват никакви превключвания. В този смисъл може да се

твърди, че структурата естествено поддържа техниката Clock Gating, известна в литературата.

Фиг. 2.5.2. Времедиаграма за край и за начало на

цикъла

В работно състояние

мултиплексорът MUX поддържа включена обратната връзка, която обхваща регистъра

фиксатор, при което след всеки импулс от сигнала Clock, комбинационната

схема Logic има възможност да изчислява нови резултати. Заедно с това в

схемата се изчислява поредната стойност на кода на условието за край на цикъла СЕС.

Ако това условие не е изпълнено (СЕС=0), изчисленията продължават. Ако

условието в текущия такт е изпълнено (СЕС=1), схемата, образувана от

двата управляващи тригера Т3 и Т4, възстановява изходното състояние на

структурата.

От изходно състояние

структурата може да бъде изведена чрез подаване на стартиращия сигнал Enable.

Той установява входния Т-тригер T1 в единично състояние (Q1=1). Правият му

изход Q1 превключва за кратко време мултиплексора MUX към входната даннова шина

Data_In по предния фронт на тактовия импулс. Така в течение на текущия период

операционната схема изчислява резултати, които са функция от тези входни данни.

В края на този такт получените и надеждно установени резултати се записват във

фиксатора. Записът се постига по предния фронт на импулса WR, който е идентичен с тактовия импулс Clock в този момент.

Импулсът е селектиран от общата последователност, с помощта на тригер T2. Освен

за запис на изчислените резултати този импулс се използва за възстановяване на

изходното състояние на тригер Т1 (Q1:=0), с което мултиплексорът отново включва

обратната връзка. Това става по задния му фронт, т.е. в момент, когато записът

на данните във фиксатора е отдавна завършил. Разнасянето (раздалечаването) във

времето на моментите на запис и превключване на мултиплексора предотвратява

възможността за състезания по обратната връзка на структурата в този начален

момент.

В края на втория такт, след

стартиране на процеса, и тригер T2 възстановява изходното си състояние Q2:=0.

Тригер Т2 се използва още за установяване на тригер Т3 в единично състояние. От

своя страна тригер Т3 се използва като маска върху тактовата последователност

на инверсната фаза на сигнала Clock. Селектираните от тази

последователност импулси се използват за запис в регистъра фиксатор на всички

последователно получени междинни резултати по време на циклическото изчисление.

Спирането на изчислителния процес в структурата и установяването й в изходно

състояние е задача на четвъртия тригер T4. Той се установява в единично

състояние синхронно по задния фронт на тактовия импулс Clock, в резултат

на появилото се условие за край на цикъла, т.е. когато CEC=1. В резултат

на това, в следващия период протича лавинообразно превключване и установяване

на тригерите T3 и T4 в изходно състояние. С това достъпът на тактови импулси

към фиксатора се прекратява и структурата се оказва в изходно състояние, като в

нея се съдържа окончателният резултат, достъпен за четене.

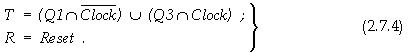

Конкретната логиката на

отделните логически връзки за управление е следната:

§

Запис на данни във фиксатора осъществяват импулсите на функцията:

![]()

§

Първият Т-тригер T1 се установява в единично състояние от

функцията

![]()

Както може да се види от

фигура 2.5.1, сигналът Enable е вътрешно временно блокиран от

дизюнкцията not(Q2ÈQ3), с което се пречи на

появата на втори стартов импулс. Този тригер T1 се връща в изходно състояние

нула по задния фронт на импулса

![]()

§

Вторият Т-тригер T2 се превключва по заден фронт от импулсите на

функцията

![]()

§

Третият Т-тригер T3 се превключва по заден фронт от импулса на

функцията

![]()

и се възстановява освен от сигнал Reset,

още от импулса (Q4 ∩ Clock), така че

![]()

§

Четвъртият Т-тригер T4 се превключва по заден фронт от импулсите

на функцията

![]()

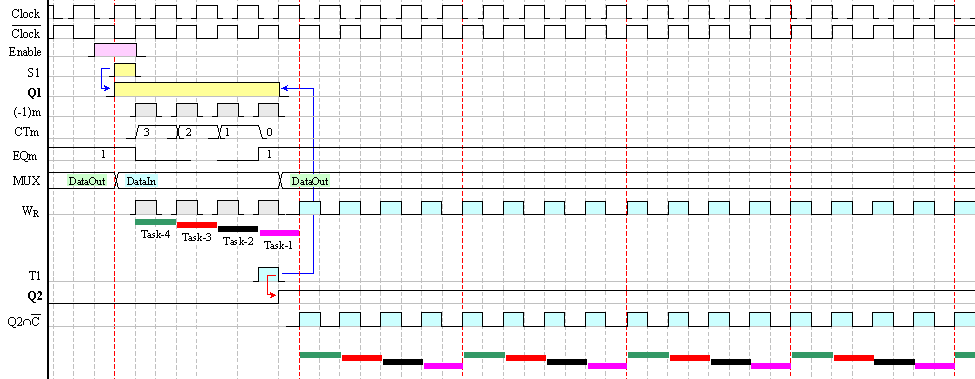

Възможността за практическа реализация

на проектираното конвейерно звено беше подложена на проверка върху

програмируеми интегрални схеми. Практическата реализация на проекта е извършена

върху програмируема матрица от серията Spartan 3 на Xilinx .

Структурата беше

реализирана като VHDL-проект в развойната среда ISE 10.1 на фирма Xilinx. Симулацията и изследването на структурата е направена с помощта

специализирания софтуер ModelSimXE III 6.2g. Поради спецификата и

конкретностите на градивните единици на логическите клетки в конкретно избраната

програмируема матрица, при създаване на реалния проект, беше използван

специфичен фирмен подход. Спецификата се изразява в строгите изисквания за

тотална синхронизация на елементите в схемата. Всички MS T-тригери, използвани

в последната обаче са асинхронни, с което се осигурява максимално бързодействие

на превключванията.

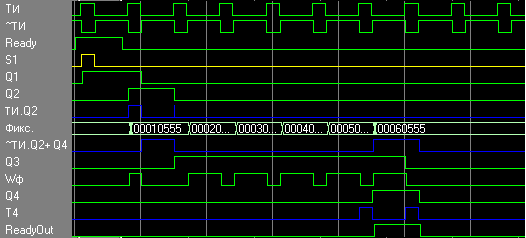

Функционирането

на моделния проект е показано на фигура 2.5.3. Аналогичното функциониране на

алгоритъма на модела доказва работоспособността на синтезираната структура, а

така също и основната теза на изследването.

Фиг.

2.5.3. Времедиаграна за функциониране на модела

2.5.2. Заключение

Циклите с отнапред

неизвестен брой повторения нямат друга алтернатива за организация, ето защо

тяхната хардуерна реализация е актуална. Като и в преди изследваните структури,

и тук, основното затруднение при синтеза произтече от използването на

единствената и еднофазова тактова последователност. Структурата е

работоспособна и представлява завършено микроконвейерно звено.

2.6. Синхронни микроконвейерни звена без вътрешни

състезания

В този раздел отново разглеждаме

циклически конвейерни звена от вида с предварително известен брой повторения, в

структурата на които се образуват вътрешно схемни състезания.

2.6.1. Въведение

Разработвайки методи за апаратна

реализация на основните алгоритмични структури, представени в началния раздел,

които могат да се срещнат по хода на даден изчислителен процес, на този етап от

изследванията, като основен проблем, на преден план излизат разнообразни

постановки на вътрешната синхронизация в структурите на конвейерните звена.

Основният метод за тяхното управление, който беше използван при техния синтез,

е синхронният. Главният мотив за този избор е простотата на синтеза. В някои от

синтезираните логически структури в подходяща комбинация са включвани логически

възли, работещи по преден или по заден фронт на тактовите импулси Clock.

С други думи, разглеждани са различни системи за синхронизация, които използват

само една от фазите на сигнала Clock или и двете едновременно – Clock и not(Clock). Това налага по време на синтеза да се използват с максимална

ефективност всички параметри на тактовата последователност. Имат се предвид

двата фиксирани от фронтовете синхронизиращи момента в рамките на един период

(преден и заден), както и коефициента на запълване, който се разбира като

следващото отношение

![]()

където с t1 е означена

продължителността на единичния импулс в тактовата последователност, а с Т е означен периодът

на същата.

С използването в

синтеза на всички споменати по-горе параметри на тактовата последователност

изследването цели да се покажат възможностите за използване на тригери с

разнообразна вътрешна структура, както и да се удовлетворят изискванията на

комбинационната логика към различните параметри на сигнала Clock.

В някои структури

обаче, тактувани с еднофазов тактов генератор, се изявяват проблеми, създавани

от вътрешните им обратни връзки. Предпоставка за това са случаите, когато

структурите са реализирани с логически възли, които се превключват по един и

същи фронт (преден или заден). Става дума за конвейерните фиксатори и

контролния брояч. В такива структури не е възможно да се постигне синхронизация

между тактовата последователност и условието за край на циклическите изчисления

(превключвания), в лицето на сигнала EQ, който се използва за управление на спирането

и стартирането на циклическите изчисления. Това е така, защото всяка нова

логическа стойност на този сигнал, като функция на новите данни, се появява с

голямо закъснение, т.е. асинхронно. В началния и в крайния моменти на този

процес, във вътрешните управляващи връзки се наблюдават състезания. В резултат

на това първият и последният записващи импулси са скъсени. Въпреки тези

вътрешни състезания структурите имат стабилно поведение. Противосъстезателните

тригери, реализиращи фиксатора и брояча, осигуряват това. Налагат се обаче

някои ограничения.

В настоящия раздел

се предлага ново решение за две такива логически структури, с помощта на което

се постига синхронизация на управлението и отстраняване на вътрешните

състезания.

2.6.2. Микроконвейерно звено за

цикъл с известен брой повторения

Логическата структура,

реализираща цикъл с известен брой повторения, представена тук в раздел 2.3, работи с вътрешни състезания от

описания вид, тъй като е реализирана с тригери, превключващи се по един и същи

(преден) фронт. Новата структура от същия вид, която е синтезирана с цел да

преодолее тези явления, е представена фигура 2.6.1.

Фиг. 2.6.1. Циклическа операционна структура,

работеща по преден фронт

На фигура 2.6.2 е

представена подробна времедиаграма на превключванията в логическата структура

при изпълнение на циклически изчисления с 12-кратно повторение, доказваща

правилността на синтезираната логика.

Фиг. 2.6.2. Времедиаграма на цикъл с 12 повторения

Представената

структура съдържа същите логически възли, но е допълнена с един синхронен RS Latch-тригер.

Задачата на този тригер е да синхронизира импулсите за запис WR и импулсите за броене (-1) с тактовите импулси от сигнала Clock.

Всъщност, този тригер не позволява на условието за край на цикъла EQ да

влияе непосредствено на логическите елементи в управляващата схема на

структурата, като го отмества във времето и организира неговото синхронизирано

въздействие.

Както се вижда от фигура

2.6.1, логиката на импулсите за запис, се изразява чрез следната логическа

функция

![]()

където с TQ е означен правият изход синхронизиращия RS-тригер.